Die ersten Berliner Schaltkreise wurden in Ost-Berlin (bis 1990 Hauptstadt der DDR) entwickelt. Produziert wurden sie im Halbleiterwerk Frankfurt/Oder (HFO), im Zentrum für Mikroelektronik Dresden (ZMD) und im Funkwerk Erfurt (FWE -> MME). Bei ersten Schritten half das Funkwerk Erfurt mit. Die DDR war damals wirtschaftlich vom Westen isoliert. Reisen in den Westen waren mir und meinen Kollegen nicht möglich. Die "Mauer" verhinderte nicht nur "Republikflucht", sondern behinderte auch wissenschaftlichen Austausch. Um unliebsames Wissen nicht in den Westen abfließen zu lassen, wurden wesentliche Entwicklungen jeglicher Art unter Geheimnisschutz gestellt. Der Ingenieur hatte unter Strafandrohung seinen Verzicht auf alle Westkontakte zu unterschreiben. Die Kehrseite war, daß man als Ingenieur, der kein NSW-Reisekader war, keine reale Chance hatte, die Relevanz technischer Entwicklungen zu beurteilen. In westlichen Fachzeitschriften wurde vieles angepriesen, von dem später nie wieder die Rede war. Selbst schriftliche Kontakte mit westlichen Wissenschaftlern wurden unterbunden. Wenn man ein Datenblatt oder ein neues, westliches Bauteil brauchte, hatte man im INT bei der Strukturbezeichnung ST (Sonderaufgaben/Technik) anzuklopfen. Und Mikroelektronik, ohne die unser Alltag heute nicht mehr denkbar wäre, wurde damals belächelt. "Ham' se schon jehört: Die jungen Leute wolln jetzt Schaltkreise entwickeln!" - "Det ick nich lache!".

Ort des Geschehens:

Im Sommer 1977 fand wieder einmal eine große Gewerkschaftsversammlung in der Kantine des INT statt. Wie immer stand die Ablösung von Edelmetallen, aber auch von Kupfer und Stahl auf der Tagesordnung. Insbesondere bereiteten der DDR die Edelmetalle Kopfzerbrechen, weil diese auch aus dem NSW bezogen werden mußten. Sowohl Valuta (Dollar, Westmark) wie auch Rubel waren kostbar. Erdgas und Erdöl konnten nur aus der Sowjetunion bezogen werden.

Weltweit waren Materialeinsparungen bei der Telefontechnik der größte Kostenfaktor. Und so hatte jede neue Generation von Vermittlungstechnik mit noch weniger Edelmetall pro Relaiskontakt auszukommen.

So wurden in der Abfolge aus Zentralen mit Drehwählern die Hebdrehwähler, daraus die Koordinatenschalter und daraus die Relais mit Reedkontakt. Damit war das Ende mechanischer Miniaturisierung der Kontakte erreicht. Wie aber sollte es weitergehen?

Der Weg führte unweigerlich zur Mikroelektronik. In der Versammlung erhitzten sich die Gemüter daran, wie das INT den Weg in die Mikroelektronik schaffen könnte. Überall war erkennbar, daß Nachrichtentechnik nicht mit kaufbaren Standardschaltkreisen (OPV, TTL, Mikrocontroller) auskommen würde. Wir brauchen kundenspezifische Schaltkreise (ASIC - Application Specific Integrated Circuits), um die analoge Relaistechnik ablösen zu können.

Nun kann aber ein analoger, d.h. die Sprache übertragender Relaiskontakt nicht einfach durch einen Transistor ersetzt werden. Transistoren haben nichtlineare Kennlinien. Sie können als Schalter für digitale Signale hervorragend eingesetzt werden. Für analoge Signale aber sind Lösungen extrem aufwendig. Möchte man den Übergang zu digitaler Vermittlungstechnik schaffen, ist die Grundvoraussetzung die Analog-Digitalwandlung (ADC) und die Digital-Analogwandlung (DAC). Diese aber bereiteten Kopfzerbrechen. Hierfür gab es keine Standardschaltkreise. Die waren selbst zu entwickeln. Nur: Wer sollte das machen? Die Firmen der DDR-Mikroelektronik hatten weder für Entwicklung noch für Produktion freie Kapazitäten.

Damals entwickelte der Autor im INT, Abt. TB4 bei Günther Warme und Bernd Grafunder an einem ersten Berliner Mikrorechner auf Basis des Intel 8008 (dessen DDR-Kopie hieß U808) mit. Der Begriff "Mikrocontroller" war damals ein Fremdwort. Niemand wußte, wozu man so etwas brauchen könnte. In Ostberlin gab es damals wohl nur zwei Teams, die sich mit so exotischen Dingen beschäftigten: Neben Günther Warmes Team gab es wenigstens noch das von Dr. Matschke geleitete Team. Der war nach der Wende einer der Gründungsväter der Technikwissenschaften an der HFÖ Berlin-Karlshorst (heute HTW Berlin-Schöneweide).

Durch die Beschäftigung mit Mikrocontrollern kamen wir deren Entwicklern im Funkwerk Erfurt (FWE, später MME) näher. So fertigten wir ab 1977 Rückübersetzungen von IC für das FWE an. Wir simulierten die Logik mit SIMPER [2].

Im Bereich von Elektronik-Entwicklungen basierte die DDR-Wirtschaft damals auf Tauschwirtschaft. Im Tausch gegen Schaltkreise, Baugruppen oder Software (Lochbänder) tauschte man Wissen und Arbeitskraft. Im Klartext: "Das INT hilft bei der Prüffolgenentwicklung und FWE bezahlt mit Naturalien dafür (Mikrocontroller und deren periphere IC)". Eine Plankennziffer bekam man natürlich nicht für irgendwelche Mindermengen neuester Schaltkreise, wie sie in Entwicklungsbereichen gebraucht wurden. In der DDR herrschte Planwirtschaft, aber kaum Marktwirtschaft.

Ausgehend vom Transistorplan der Z80-Schaltkreise vom FWE erstellte der Autor gegen 1977 Logikpläne und Logikbibliotheken. Dabei entstand eine erste SIMPER-Modellbibliothek [2] für die Logiksimulation für U880 PIO (U855) und CTC (U857). SIMPER war der damals leistungsfähigste Logiksimulator in der DDR. Er kam aus dem INT von den Kollegen um Herrn Dr. Werrmann und Herrn Schalldach in der INT-Außenstelle Altglienicke, Baracken Ewaldstr. 68-82, siehe auch Anmerkung (2).

Weitere Kollegen stießen hinzu. Manfred Hanel und Joachim Feierabend vom Bereich Vermittlungstechnik (V) entwickelten mit unseren Logikplänen die Prüffolgen für Z80 PIO und Z80 CTC. Joachim Feierabend diplomierte 1979 mit einem Prüfgerät für die U855 PIO.

Bild 1a: U855 (Z80 PIO) und U857 (Z80 CTC) des FWE/MME im Gehäuse

Allerdings hatte SIMPER ein Problem. Bei MOS-ED-Schaltungen (MOS-Enhancement-Depletion ~ nSGT oder NMOS) waren mehrfache Open-Drain-Gatter sehr beliebt. Praktisch alle Mikroprozessoren liefen damit in NMOS (nSGT). NMOS war schneller als PMOS, hatte eine vierfach höhere Packungsdichte als CMOS (CSGT) und bot eine viel höhere Entwurfssicherheit als I²L.

Beim Open-Drain-Gatter wird eine Leitung von einem "Pull-Up" Widerstand (als Depletion-Transistor) statisch (auf VDD ~ logisch High oder "1") hochgezogen: Die Leitung kann aber von Enhancement-Transistoren in verschiedenen Baugruppen herunter gezogen werden (z.B. zur Auslösung eines Interrupts, eines Resets etc.. SIMPER kannte diesen Gattertyp nicht. Die Logikmodellierung entwickelte sich damit zum Albtraum. Fehler über Fehler entstanden. Und der Logikplan hatte anschließend nichts mehr mit dem Layout gemein [2], er wurde unübersichtlich und fehlerbehaftet.

Erst mit der Fertigstellung des LSI-Simulators (3) [5] der Kollegen um Franz Rößler und Wolfgang Hecker in Erfurt entfiel dieser fehleranfällige Zwischenschritt der Konvertierung der Transistorschaltung in die Logikschaltung. Der LSI-Simulator arbeitete auf Transistor-Ebene (als Schalter-Simulator) statt mit Logikgattern. Er gestattete die direkte Eingabe des Transistorplans. Dieser konnte damit ohne Konvertierungsfehler simuliert werden.

Auf einem Ausschnitt der Rückübersetzung finden sich Fragezeichen: Wir wußten zunächst nicht, um welchen Schaltkreis es sich eigentlich handelte, der spätere Favorit Z80 war für uns zu weit weg. Aus damaliger Sicht sprach mehr für den Intel 8253, die Zilog CTC dürfte eigentlich gerade erst auf den Markt gekommen sein. Da wir das Layout nicht kannten (wir hatten von Erfurt nur die Netzliste erhalten), wußten wir zunächst nicht, woran wir arbeiten. Unser Input waren mehr oder minder konfuse Transistorpläne. Die Notiz "Z80-CTC" auf dem Logikplan wurde von mir erst später nachgetragen, als ich ahnte, daß dieser irgendwo privat abgelegte Logikplan vielleicht einmal interessant werden würde.

Wie wir heute wissen, hatte man im RGW auf die Intel 8080-Serie gesetzt. Die DDR aber ließ sich ganz schnell von den Vorteilen des Zilog Z80 Systems überzeugen (nur eine Betriebsspannung, internes dRAM-Refresh, nette Interrupts etc.). Die RGW-Linie aber war das schon vorher auf den Markt gekommene Intel 8080 System. Die DDR wich somit vom rechten Weg ab. So stieß die spätere Verwendung des Zilog Z80-Systems in NZ400-Zentralen für die NVA beim "großen Bruder" zunächst auf Unwillen. Erst später setzte sich das Z80-System auch RGW-weit durch.

Produktionsbeginn der U880 Schaltkreise war 1980. Erstaunlich schnell, wenn man bedenkt, daß Zilog den Z80 selbst erst im Juli 1976 auf den Markt brachte. Wir standen unter Hochdruck.

Bild 1b: Teil der Rückübersetzung vom Zilog-CTC des Autors. Rechts Teil des Schaltplans des U857 (um 1978), links ein Auszug davon. Die Schrift ist die des Autors. Der IC wurde im INT für die Generierung von Prüffolgen aufbereitet. Man beachte die geniale Logik der Binärteiler.

Der im Präsidium sitzende Technologiedirektor des INT Dr. Lothar Auer antwortete: "In meiner Abschlußarbeit auf der Parteischule ... kam ich genau zum selben Schluß: Wir kommen nicht daran vorbei, uns selbst zu helfen.

Sie (er zeigte auf mich) sind morgen früh um acht Uhr bei mir, dann besprechen wir, was zu tun ist!"

Am nächsten Morgen schmiedeten wir Pläne. Er hatte erfahren, daß an der TU Dresden ein postgraduales Sonderstudium "Mikroelektronik" eingerichtet werden soll. Ich schaute mir die Unterlagen an, war begeistert und meldete mich an. Vom 12.9.77 bis 31.5.1978 fuhr ich alle vier Wochen für eine Woche in ein Studentenwohnheim an der Prager Straße (heute St. Petersburger Str. 25) nach Dresden, dort brachten uns die Spitzenkräfte der TU Sektion 9 (Informationstechnik) die Grundlagen des Schaltkreisentwurfs bei, siehe auch das Zeugnis.

Prof. Groß, Prof. Wolfgang Albrecht, Prof. Dieter Landgraf-Dietz, Prof. Albrecht Möschwitzer (Fach "Mikroelektronik") und Prof. Horst Elschner gaben die Praxis von Transistormodellierung, Layoutentwurf, Netzwerk- und Logiksimulation, Prof. Cimanders Assistent gab das Fach "Mikrorechner" (der Professor selbst verstand noch nichts davon) und Prof. Karl-Heinz Diener lehrte im Fach Halbleiterelektronik die spezielle Feldtheorie - die Berechnung von Raumladungszonen und Halbleiterübergängen.

Bedauerlicherweise wird diese geschichtliche Ära enormen Wissenszuwachses an der TU Dresden heute historisch vollkommen ausgeblendet, [9]. Der Fortschritt der DDR-Mikroelektronik war ohne diese Experten in Dresden undenkbar. Nach der Wende entwickelte sich Dresden zum führenden Mikroelektronik- Standort Europas - kein Zufall. Umso bedauerlicher ist es, daß man von den damaligen Experten, insbesondere von Albrecht Möschwitzer, nicht einmal eine Biographie oder ein Foto auf der Homepage der Sektion 9 der TU findet.

Bei Albrecht Möschwitzer wurde dann eine Abschlußarbeit geschrieben: Ich hatte einen 5-Bit Gebührenzähler für Telefonanlagen zu entwerfen, wenig zeitgemäß noch in PMOS-Hochvolt-Technologie mit negativer Betriebsspannung von -30 Volt. Das Layout wurde im Maßstab 1000:1 gezeichnet, 1 Mikrometer entsprach einem Millimeter auf dem Papier. Leider sind weder Layout, noch schriftlicher Teil erhalten. Wahrscheinlich stand gerade wieder keine Kopiermöglichkeit zur Verfügung. Im Bild sind die komplizierten PMOS-Entwurfsregeln zu erahnen:

Bild 1c: Links: Entwurfsregeln der 1978 schon veralteten EE-PMOS-Hochvolttechnik im Maßstab 1000:1 (1 mm ~ 1 m). Rechts: Schaltplan des Gebührenzählers

Jedesmal zitterten einem die Knie, wenn man zu Möschwitzer vorgeladen wurde. Er war der Pabst der DDR-Mikroelektronik jener Zeit. Ähnlich wie Karl Nendel hatte Albrecht Möschwitzer ohne Rücksicht auf persönliche Belange eine ätzend geradlinige Art, in atemberaubender Geschwindigkeit auf den Punkt zu kommen. Es war begeisternd, mit ihm - stets in kürzester Zeit - fachliche Probleme zu diskutieren. Auch Franz Rößler, der spätere Chefentwickler des FWE hatte bei Möschwitzer promoviert.

Die PMOS-Gatewanne war noch nicht selbstjustierend wie bei Intels Silicon-Gate-Technologie (SGT) des Intel 4004 [10] aus dem Jahre 1971, sie mußte separat gezeichnet werden. Das hatte Konsequenzen für die Ausbeute. Verrutschte die Gatewannen-Maske nur um zehntel Mikrometer, funktionierten die IC des Wafers nicht mehr. Auch sank erst mit den Silizium-Gates die Schwellspannung der Transistoren, erst damit konnte die Betriebsspannung der IC verringert werden. Nach meiner Erinnerung hatten die PMOS-Transistoren eine typische Schwellspannung von -3Volt (+/- 20%).

Insofern entstand erst durch die Einführung der selbstjustierenden Polysil-Gates mit der Silicon-Gate-Technology die Möglichkeit, wesentlich kleinere Strukturen fertigen zu können. PMOS war wirklich noch MOS (Metall-Oxid-Silizium). Über dem Gateoxid lag Aluminium als Gate. Allgemein vergessen: Erst die von Fairchild schon 1968 eingeführte SGT ermöglichte die Entwicklung unserer heutigen Mikroelektronik.

Damals existierte noch ein erbitterter Technologiestreit zwischen bipolar (SBC, I²L) und unipolar (PMOS, nSGT, CSGT) Technologien, der auch an der TU Dresden immer wieder zu heftigen Debatten führte. Mit I²L ließ sich eine vielfach höhere Packungsdichte als mit MOS erzielen, dafür verbrauchte MOS viel weniger Ruhestrom. Insbesondere aber die Frage der Verkopplung von Fan-Out und Stromergiebigkeit des treibenden Transistors führte zu zusätzlichen Problemen beim I²L-Entwurf, sodaß MOS-Technologien die Oberhand gewannen.

Letztlich setzten sich für erste Taschenrechner und Prozessoren pSGT-HV (Hochvolt) durch, zum Beispiel beim Intel 4004 (mit minus 15 Volt). Etwa ab 1975 kam der Siegeszug der nSGT (n-channel Silicon-Gate) Technik mit 5 Volt Betriebsspannung. Vom Flächenverbrauch lag nSGT in der Mitte zwischen I²L und CSGT (CMOS) (Intel 8080, Zilog Z80 etc.). Erst Mitte der 80-er Jahre wurden die Strukturgrößen so klein, daß die statisch verlustfreie, aber mehr als doppelt so flächenintensive CMOS-Technologie (CSGT) ihren universellen Siegeszug antrat und die nSGT langsam ausstarb.

Als der erste (marktgängige) Mikroprozessor Intel 4004 im Jahre 1971 herauskam, flogen Menschen noch zum Mond. Seither werden die Innovationen wieder kleiner. Denken wir an Genderwahn, Gendersprech, Corona-Lockdown, Kernkraftwerkszerstörung, Energiewende und E-Mobilität scheint es mir, als hätte die Menschheit ihren intellektuellen Gipfel bereits überschritten.

Starthilfe vom Funkwerk Erfurt (FWE/MME)

Eigentlich begann alles mit dieser Kooperation mit dem FWE. Wir wollten lernen, wie man Schaltkreise entwickelt, um später eigene zu entwickeln. Vom FWE bekamen wir die Chance, einen ersten, eigenen Mikrocontrollerbaustein zu entwickeln. Im Gegenzug hatte das INT den Logiksimulator Simper (2) zu bieten, der interessierte die Entwerfer des FWE solange, bis sie mit ihrem eigenen "LSI-Simulator" (3) [5] arbeiten konnten.

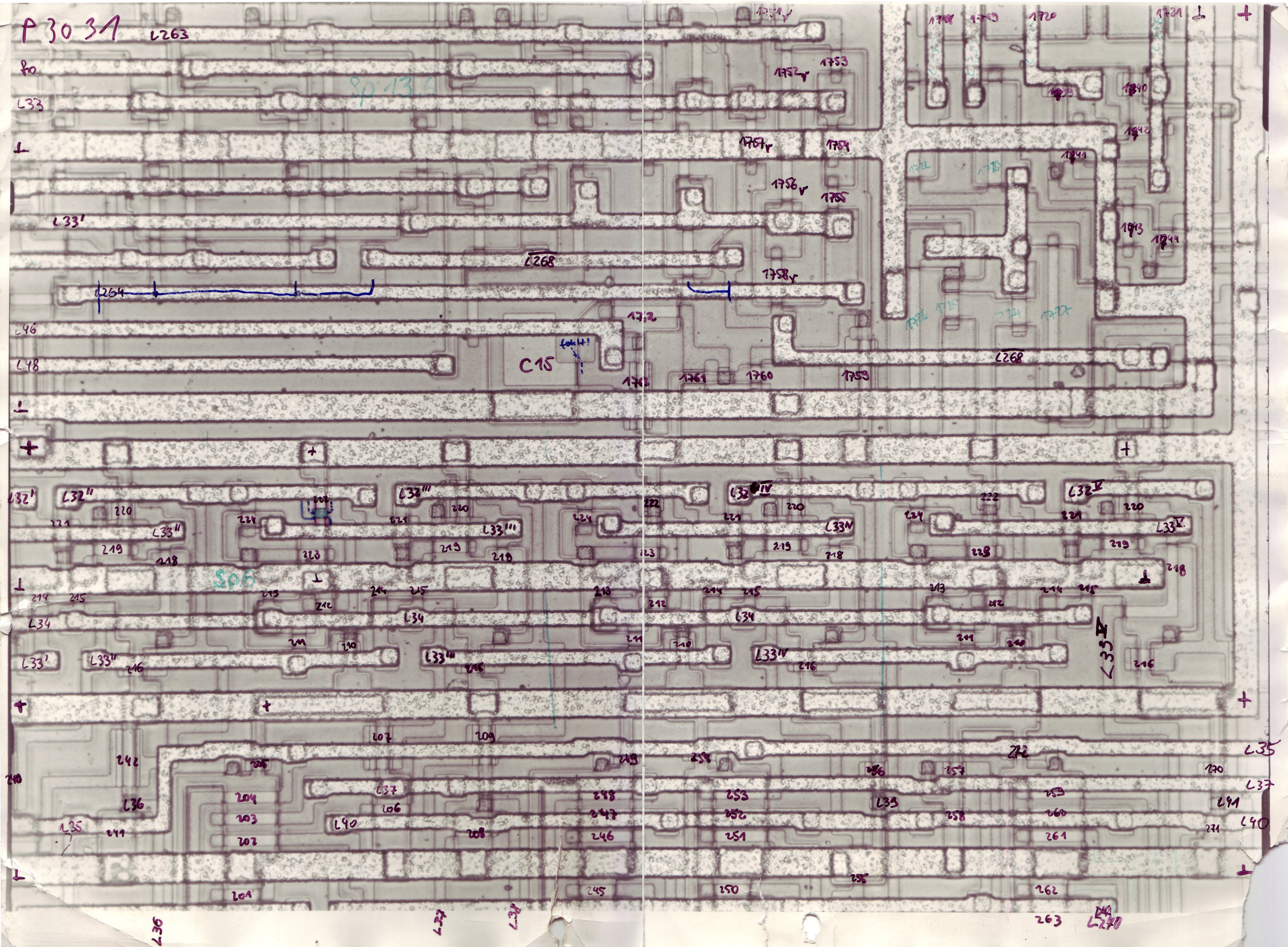

Vielleicht nahm uns Franz Rößler (1) auch nicht wirklich ernst. Im September 1979 bekamen wir Fotos eines geeigneten Übungs-IC, des Tastatur- und Anzeigedecoders Intel 8279 sowie passende nSGT-Entwurfsregeln. Aufgefundene Folien [1] erinnern daran. Der Autor übersetzte das Layout in die Transistorschaltung zurück. Auf der Rückseite notierte ich: "Rückübersetzung 1979/1980, 4500 Transistoren, 14-tägige Heimarbeit 23. Oktober bis 2. November 1979 (allein zu Haus mit einjähriger Tochter)".

Der Transistorplan war nach den Layout-Fotos (siehe Bild 3) willkürlich durchnummeriert. Daraus war ein Logikplan für die Logiksimulation mit SIMPER (2) zu rekonstruieren. Die zwischen den Detailfotos (Bild 3) liegenden Transistoren hatten verschiedene Nummern, sodaß ein einziges Logikgatter vollkommen unterschiedliche Transistornummern haben konnte. Es war eine haarsträubend komplizierte Aufgabe darin die Logik zu erkennen, auch weil Fehler nicht vorkommen durften.

Der IC war in nSGT realisiert (nSGT: n-Enhancement und n-Depletion Transistoren, auch als NMOS-ED-Technologie bezeichnet). Daraus konnte Uli Diedrich die Logikpläne für SIMPER [2] rückübersetzen (2), siehe Bild 4.

Was wir dabei lernten, war wertvoll. Wir bekamen eine Vorstellung vom Layoutentwurf, von nSGT-Schaltungstechnik und von Transistormodellierung. Wir bemerkten, daß Intel den 8279 wohl mit gravierender Manpower gemacht hatte - über die wir nicht annähernd verfügten (meine damalige Schätzung zum 8279 lag bei 50 Mannjahren). Vergleicht man das Layout des 8279 mit dem des Intel 4004, dann wird bewußt, daß sich die IC in der Designeffiziens bereits unterscheiden. So hatte der Intel 4004 etwas klarere Wiederholstrukturen. Er dürfte mit einem Bruchteil der Mannpower des 8279 ausgekommen sein.

Mead/Conway [3] brachten 1979 mit dem Buch "Introduction to VLSI-Systems" den Gedanken der Zeitersparnis durch Wiederholstrukturen zum internationalen Durchbruch. Der hervorragend strukturierte Entwurf des OM2 Data-Path-Chips des Studenten David Johannsen war revolutionär.

1980 besorgte der Kollege Dr. Karl-Adolf (Ali) Zech neben anderen Veröffentlichungen auch das Buch aus den USA, nur wenige Kopien von schlechter Qualität konnten unter IC-Designern der DDR verbreitet werden. Kopiertechnik war rar. Ali schrieb Rezensionen für Fachzeitschriften und bekam dadurch Belegexemplare.

Mit dem Scheme-79 Chip von Holloway, Steele, Sussman und Bell [11] wurde die Mead/Conway Methode fortgesetzt. 1980 konnte das Layout eines LISP-Prozessors (Lisp-Dialekt SCHEME) durch Wiederholstrukturen extrem vereinfacht werden (im Bild 2 rechts). PLA- und ROM-Strukturen machten es möglich. Gegenüber dem wenige Jahre vorher entstandenen Übungsschaltkreis (links im Bild 2) dürfte der Entwurf Zehnerpotenzen an Zeit eingespart haben (wahrscheinlich zu Lasten einer verkraftbar geringeren Taktrate).

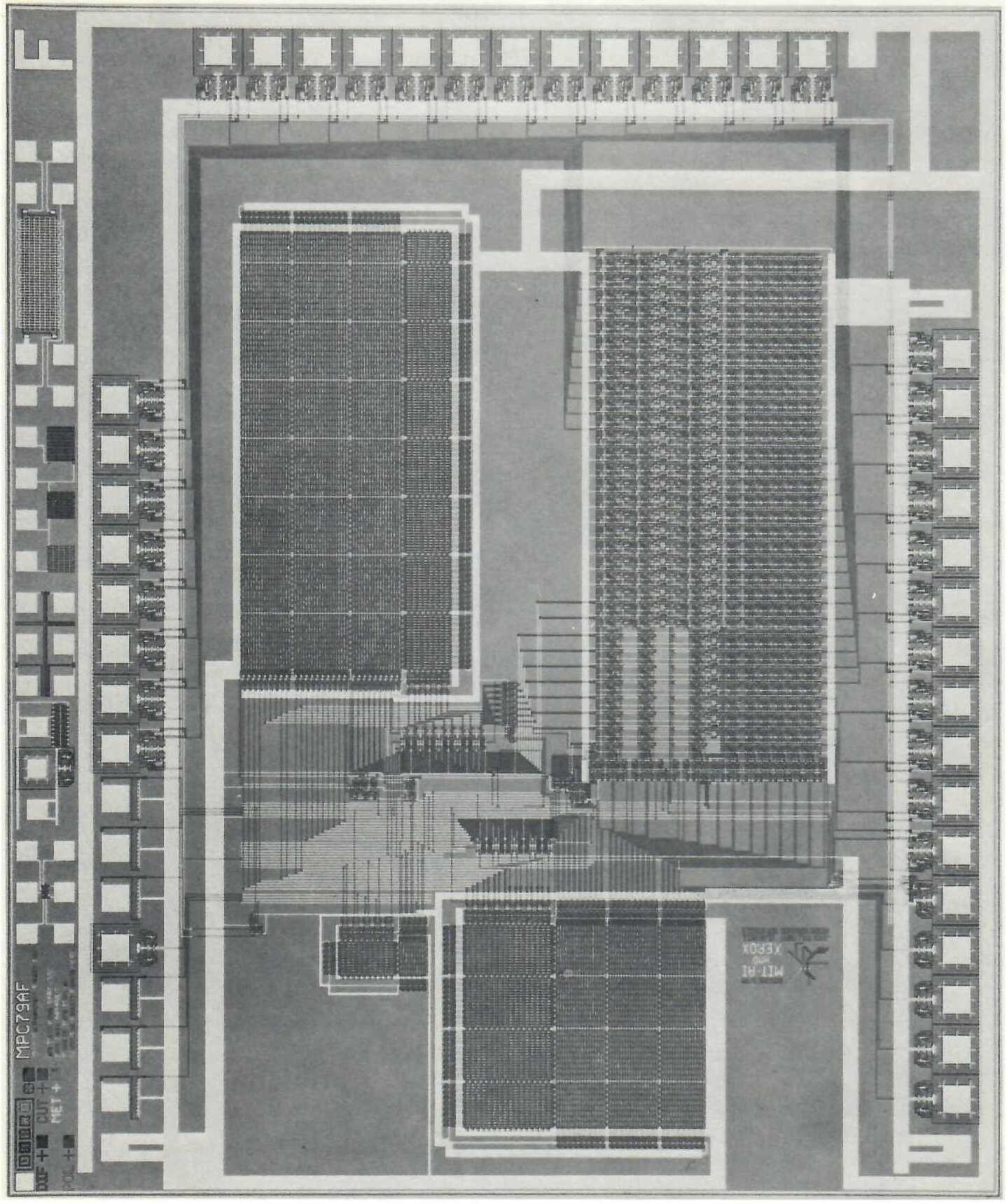

Bild 2; Links: Übersichtsfoto für die Rückübersetzung des Übungsschaltkreises 8279 (seitenverkehrt). Jede rote Nummer gehörte zu einem Detailfoto im Format A3. Es entstanden 7x10 Fotos im Format A3. Das Layout war im Funkwerk Erfurt fotografiert worden.

Rechts: Zum Vergleich die Design-Revolution von 1979/80: Layout des SCHEME-79-Chips [11] zum Titelblatt von [6]

Im Gegensatz zur BRD unterschied man in den USA und in der DDR begrifflich zwischen MOS (Metal Oxid Silicon) und SGT (Silicon Gate Technology), MOS gab es nur zu Anfang als PMOS, danach gab es ausschließlich selbstjustierende (polymorphe) Silizium Gates - SGT (weltweit). Schon der Intel 4004 Prozessor hatte im Jahre 1971 selbstjustierende Gates, er war in p-Kanal SGT (pSGT) mit (eigentlich) negativer Betriebsspannung und aus heutiger Sicht negativer Logik gefertigt. Um mit TTL oder nSGT kompatibel zu werden, war ein Trick erforderlich: GND des pSGT-Chips ist auf +5 Volt, VDD auf -9 Volt zu legen. Allerdings werden damit auch alle Signale invertiert, aus "1" wird "0" und umgekehrt.

Bild 3: Eines der 70 Detailfotos des Übungs-IC im Format A3. Die Rückübersetzung geschah in 14-tägiger Heimarbeit im November 1979. Man erkennt im Bild die blinde Durchnummerierung der Leitbahnen (L...) mit den darunter liegenden blind nummerierten Transistoren.

Ab und an ist der vermutliche Verlauf von Polyleitungen (polykristallines Silizium) unter dem Alu blau nachgezeichnet. Um Platz zu sparen, wurden die Transistoren (Logikgatter) in genialer Weise manuell unter die Leitbahnen "gequetscht". Man sprach von "Gummizellen-Design". Das Zeichnen des Layouts eines einzigen Gatters brauchte extrem viel Zeit und Manpower. Und jedes Gatter - auch wenn es vom selben Typ wie der Vorgänger war - war neu zu zeichnen und neu zu prüfen.

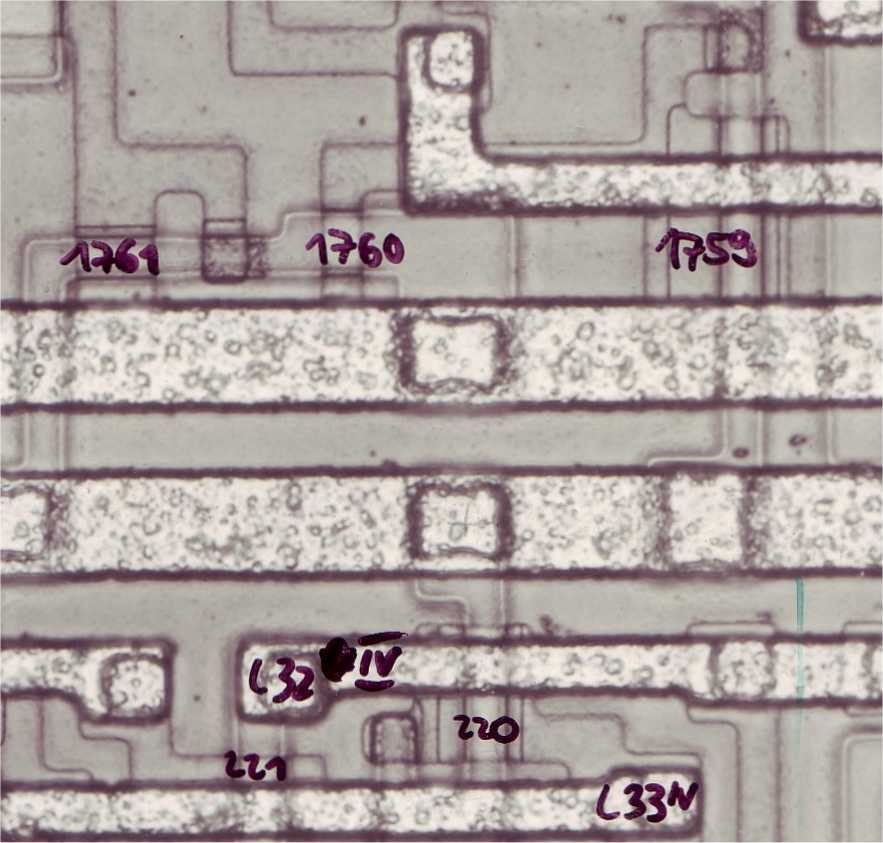

Bild 3a: Ausschnitt aus Bild 3. Man erkennt einen Enhancement-Transistor 1760 sowie einen Depletion-Transistor 1761. Zusammen bilden sie einen Inverter, dessen Ausgang nach links oben zeigt. Der Source-Anschluß des Enhancement-Trs. liegt auf 0V (GND), der Drain des Depletion-Transistors auf +5V (VDD). Damit sind VDD und GND bereits bekannt.

Wichtig war in diesem Zusammenhang, daß Open-Drain-Schaltungen nur über Alu-Leitbahnen gekoppelt werden konnten, Poly-Leitungen hätten einen zu hohen Spannungsabfall verursacht, sie konnten nur für statisch stromlose Eingänge (Gates) genutzt werden, niemals für "verteilte" Gatter in Open-Drain Schaltungen (wired OR). Wenn man genau hinschaut, erkennt man die horizontale Signalrichtung der "langen" Alu-Leitbahnen. Die "kurze" oder Gate-Richtung ist vertikal im Polysil zu erkennen.

Um das Layout zu verstehen, orientiere man sich an den von links und rechts kommenden VDD- und GND-Fingern. Dazwischen befinden sich die Gatter dieser Reihe entsprechend den Entwurfsregeln in [1]. Allein die Rückübersetzung der siebzig A3-Layoutfotos kostete in Heimarbeit mehr als zwei Wochen - von früh bis spät. Dabei entstanden zunächst 'zig Dutzend A4-Blätter mit Gattern, die genau so anonym nummeriert waren, wie die Fotos. Im nächsten Schritt waren die Zuordnungen der Gatter zu Baugruppen zu ermitteln. Diese Aufgabe kam Uli Diedrich zu. Ich begann schon mal mit der Entwicklung eines PCM30-Regenerators.

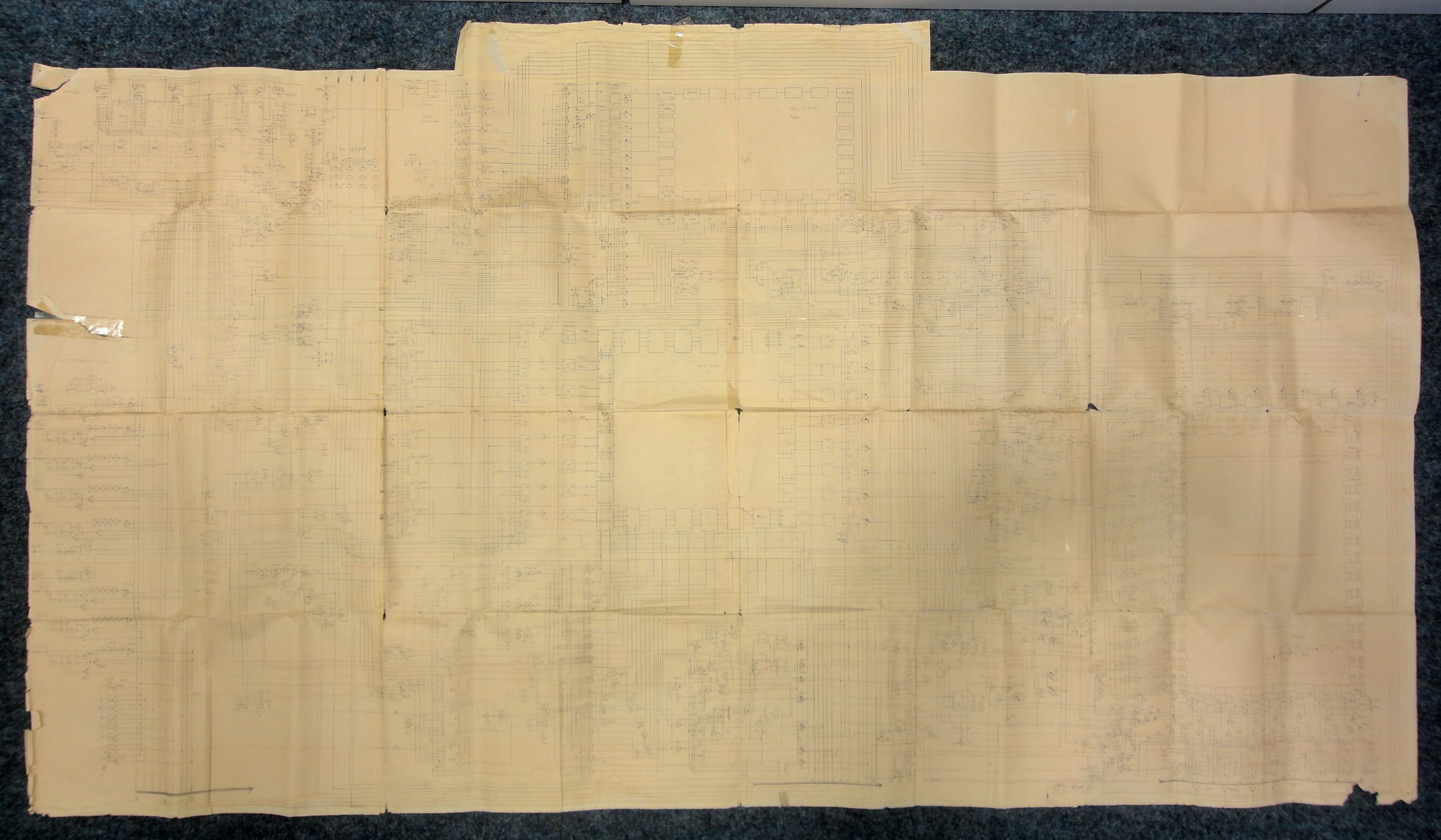

Bild 4: Von Uli Diedrich in 6 Monaten rückübersetzter Logikplan des Übungsschaltkreises mit 4500 Transistoren.

Kollege Uli Diedrich erstellte den folgenden Logikplan aus meinen rückübersetzten Transistorplänen der Seiten. Er arbeitete ein halbes Jahr daran. Meine Transistorpläne der Detailfotos waren sein Input. Kein einziger Fehler war erlaubt. Eine Knochenarbeit, ein zermürbender Job. Uli kündigte nach dieser Arbeit und wurde Leiter eines Jugendklubs in Mecklenburg. Besondere Probleme bereiteten die Wired-Or-Verbindungen, SIMPER kannte nur kompakte Gatter als Bauelemente. So hatte man die Wahl, den Schaltplan Layout-konform zu gestalten, oder SIMPER-gerecht. Erst der LSI-Simulator (3) aus dem FWE [5] beendete die zwingende, Verwirrung schaffende Schaltungs-Umformung in Logikgatter.

Ich schrieb später einen Aufsatz [6], um auf das Entwurfsproblem und auf den effizienteren Entwurfsstil [3] von Mead/Conway und deren Studenten aufmerksam zu machen. Herkömmliches Gummizellen-Chip-Design (Bild 3) brauchte vielleicht um die 50 Mannjahre, Meads Student David Johannsen mit dem OM2 Data-Path-Chip von 1977 (in der Umschlagseite von [3] abgebildet) wie auch der SCHEME-79 chip [11] von Holloway und Kollegen von 1980 wurden in wenigen Monaten entworfen.

Die Zeit der Gummizellen war mit Mead/Conway vorbei, aber das war erst zwei Jahre später. Neue Ideen waren gefragt. Die Zeit der CMOS-Standardzellen, der Makrozellen und der Building Blocks kam näher. Zehn Jahre später bestand ein Layout nur noch aus rechteckigen Moduln, die auf allen Seiten Kontaktanschlüsse aufwiesen. Immer weitere Skalierung der Leitbahnen machte es möglich.

Auch auf einen anderen Aspekt der Arbeiten am Multi-Project-Chip (MPC) wäre noch zu verweisen, Bild 5. Mit dem MPC-Projekt sorgten seit 1978 US-amerikanische Mikroelektronikfirmen für einen Innovationsschub, der ein viertel Jahrhundert lang anhielt. Hatten wir im RGW bis zur Wende (1989) etwa 1500 Schaltkreistypen entwickelt, waren es vorrangig in den USA etwa eine halbe Million Typen. Dahinter steckte eine riesige Anzahl von Designern, die als Studenten mit einem eigenen IC innerhalb eines MPC erste Schritte machen konnten. Ebenso wichtig war das praktische Ausprobieren neuer Schaltungsideen.

Mein Aufsatz [6], [12] wurde blockiert wegen der "Tafel 2: Teilnehmer am MPC-Projekt" (MPC: Multi-University Multiproject Chip-Set Project) [13]. Das Argument des Sicherheitsbeauftragten des INT Stasi-OibE Gerhardt dazu lautete: "Nicht von den Amerikanern lernen heißt siegen lernen, sondern von der Sowjetunion lernen heißt siegen lernen! Die Tabelle geht raus". Alle Argumente halfen nicht. "Die Zeitschrift wird mit dieser USA-Werbung nicht erscheinen!" Sie erschien aber doch. Den Rest der Geschichte kann man hier nachlesen: [12]. Man hätte den Autor dafür beinahe inhaftiert. Ein U-Haft-Einlieferungsschein fand sich in den Stasi-Unterlagen.

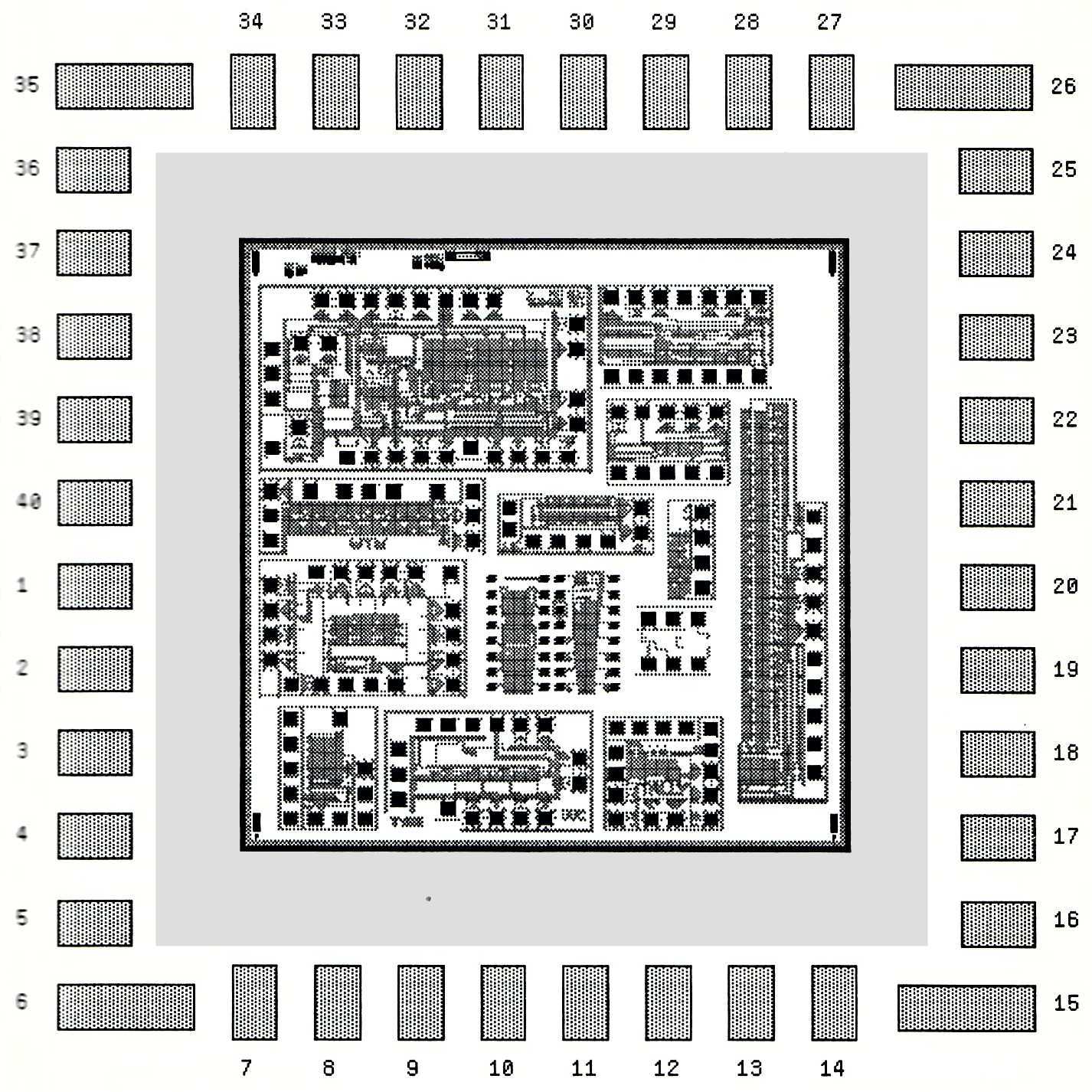

Bild 5: Beispiel eines Multi-Project Chips (MPC Wire Bonding Map) [14], ergänzt nach Fig.5.3.1, S.43. Die vereinzelten MPC-Chips wurden hier in ein 40-poliges Keramik-Standardgehäuse mit Silber-Epoxydharz eingeklebt. Mit einem Ultraschall-Bonder konnte dann der Teilnehmer seinen Entwurf manuell anschließen.

Das erste MPC-Lehrbuch zu Fragen der Technologie der Entwicklung und Fertigung eines mikroelektronischen Schaltkreises erschien zum Sommerkurs des ersten MPC-Projekts 1978. Die zweite Auflage [14] erschien im Januar 1980 mit einem Vorwort von Lynn Conway mit dem Hinweis auf das Buch "Introduction to VLSI-Systems" [3].

Im Gegensatz zum MPC-Projekt war unser postgraduales Sonderstudium 1977/1978 bei Prof. Möschwitzer eher von theoretischer Natur. Für praktische Fragen fehlten Ausrüstungen. Die Abschlußarbeit, beim Autor der Entwurf eines Gebührenzählers in veralteter PMOS-Technologie, wurde mit Bleistift auf Millimeterpapier gezeichnet. An Rechentechnik stand 1978 an der TU Dresden nur eine BESM-6 mit Lochkarteneingabe, Fernschreibern und Druckern zur Verfügung. Damit konnten allenfalls kleine elektrische Netzwerksimulationen gemacht werden.

Zurück zum MPC-Projekt. Es ist heute noch eine Freude, Hon und Sequin [14] noch einmal zu lesen. Hier werden dutzende praktische Probleme im Detail besprochen, so daß man auch nach 30 Jahren noch staunt. Beginnend bei der Layoutsprache CIF über Netzwerksimulation, Bonden und Verkappung bis zum Test wird alles allgemeinverständlich angerissen. Im Grunde ist es ein Lehrbuch darüber, wie ein Entwicklungsland eine Mikroelektronikproduktion aufzubauen hat. Hon und Sequin bedanken sich übrigens im Vorwort von [14] für die großzügige finanzielle Unterstützung von Xerox, der Carnegie-Mellon-University und dem Department of Defense (DoD).

Während Mead/Conway's Buch im Westen gefeiert wurde [15], stand Karl-Adolf (Ali) Zech unter ständiger Stasi-Beobachtung. Er pflegte dennoch seine Kontakte zu US-Universitäten und erhielt dutzende hochbrisanter Forschungsarbeiten, wie zu OPV-Entwicklungen, zu ADCs, zu CCDs oder zum GPS. Immer wieder konnte der Autor interessante Arbeiten bei ihm ausleihen.

Danach wurde der Autor stets vom Leiter der Abteilung ST, Günter Dumont energisch aufgefordert, alle Kontakte zu Dr. Zech sofort abzubrechen. Ali stand offenbar unter ständiger Beobachtung durch die Staatssicherheit. Eine unausgesprochene Drohung stand im Raum, schließlich war mein leiblicher Vater vor dem Mauerbau 1961 nach Westberlin geflüchtet. Meine Mutter hatte den Kontakt damals abgebrochen, seine Adresse war mir unbekannt. Auch ich stand damit unter Beobachtung. So hatte ich als Geheimnisträger in halbjährlichen Abstand immer wieder eine Aufstellung meiner Westkontakte vorzulegen.

In anderen Ländern wäre man glücklich gewesen, einen so erfolgreichen Beschaffer hochbrisanten Wissens wie Ali Zech fördern zu können. Nicht so in im INT. Ali wurde gemobbt, bis er 1983 frustiert das INT verließ und zum Werk für Sicherungstechnik und Signalbau in die Elsenstraße wechselte. Eine Zusammenarbeit mit der Stasi kam für ihn aus moralisch-ethischen Grundsätzen prinzipiell nicht in Frage [12]. Auch war er in der Kirche aktiv und wagte es, mit einem aufgenähten "Schwerter zu Pflugscharen" Abzeichen im Institut zu erscheinen. Er erhielt dafür ein Hausverbot.

Unser Übungsschaltkreis wurde nicht ins Layout gebracht. FWE hatte neue Prioritäten, das INT sowieso. Dennoch war es eine nützliche Kooperation. Wir lernten Erfahrungsträger in Erfurt kennen und bekamen eine Vorstellung davon, wie man Schaltkreise entwickelt. Mit den Erfahrungen aus diesem Knochenjob und mit den Erkenntnissen Mead/Conways gewappnet, entstand 1981 der Aufsatz "Grundzüge des höchstintegrierten Schaltkreisentwurfs (VLSI)" [6].

Letztlich aber gab es dadurch einen Ruck. Parteileitung (SED) und Gewerkschaftsleitung konnten von Dr. Bogk und der Institutsleitung überzeugt werden, die Ressourcen freizugeben zur Gründung eines Entwurfszentrums Mikroelektronik. Dazu mußten qualifizierte Mitarbeiter gefunden werden, man brauchte Räume und Mittel für Ausrüstungen und Lohn. Die waren nicht im Fünfjahresplan vorgesehen. Unsere Gehälter waren damit die kleinsten des Instituts, auch Rechentechnik kam kaum an - aber alle warteten auf unsere Schaltkreise.

Um es abzukürzen: Das Entwurfszentrum Mikroelektronik (EZµE) des INT wurde mit einem feierlichen Akt am 19.12.1979 vom frisch promovierten, von der TH Magdeburg gekommenen und als Hauptabteilungsleiter TB eingesetzten Dr. Dietmar Bogk gegründet. Und Dr. Ingomar Krahl war wohl der erste Mitarbeiter, den Dr. Bogk als neuen Abteilungsleiter TB4 einstellte.

Ingomar Krahl brachte aus der Sektion 9 der TU Dresden hervorragendes Wissen insbesondere zur Transistormodellierung (Ebers-Moll und Gummel-Poon) [17], zur SBC-Schaltungstechnik (Standard Burried Collector) und zur I²L-Schaltungstechnik (Integrated Injection Logic) mit. Insbesondere seine exzellenten Kenntnisse zur Transistormodellierung halfen enorm beim Aufbau einer ersten Modellbibliothek für die Netzwerkanalyse mit STADYNET sowie bei der Entwicklung des ersten Schaltkreises des INT, dem PCM30-Regenerator KA601 des Autors. Dieser sollte im (militärischen) Temperaturbereich von -40°C bis +85°C arbeiten. Netzwerksimulationen im Temperaturbereich waren substanziell.

(1) Prof. Dr. Franz Rößler, Chefentwickler im Funkwerk Erfurt, Schüler und Freund Albrecht Möschwitzers, war aus meiner Sicht der wichtigste Motor der Entwicklung von Mikrocontroller-IC in der DDR.

(2) SIMPER war zum Ende der 70er Jahre der leistungsfähigste Logiksimulator der DDR. Er kam aus dem INT (Dr. Günther Werrmann, Hans-Henrich Schalldach u.a.). Simper wurde anfangs entwickelt auf einem IBM360/40 im ORZ des Bauwesens ZOD (Charlottenstraße). Dr. Karl-Adolf Zech schreibt dazu: "Irgendwann begann SIMPER mit Lochkarten und zunächst spaltentreuer Eingabe der Daten, weil wir die Eingabeschnittstelle vom Bereich T übernahmen, die sie hatten zum Leiterplattenentwurf; später auf Wunsch des ZKI Dresden ohne starre Spalteneinteilung. Irgendwann wurde aus IBM der hauseigene ESER 1040 (Nachbau des IBM360)." Erste Logikmodelle zur Schaltkreissimulation (Gatter, Flipflops) kamen vom Autor [2].

(3) Der LSI-Simulator [5] spielte aus der Sicht des Autors die wesentlichste Rolle beim Entwurf der Mikroprozessor-Schaltkreisserien in Erfurt, wie auch beim Entwurf der nSGT-Schaltkreise für das Digitale Vermittlungssystem (DVS) im INT.

Im LSI-Simulator kamen zwei neue Ideen zum tragen. Einerseits die von Franz Rößler schon in der Dissertation bei Prof. Dr. Albrecht Möschwitzer (damals TU Dresden, Sektion 9, Informationstechnik) entwickelten Programme des LSISIM-Komplexes, um den Maskendatensatz (Layout) gegen die Transistor-Netzliste prüfen zu können. Und zweitens der von Wolfgang Hecker in der Dissertation entwickelte Simulator LSINET, bei dem die Transistoren der Netzliste als Schalter abstrahiert wurden. Durch die Schalterdarstellung wurden Fehler bei der Umformung der Netzliste in Logikgatter (Logikmodelle) vollständig vermieden. Insbesondere Open-Drain-Schaltungen ließen sich mit klassischen Logiksimulatoren, wie SIMPER, kaum fehlerfrei simulieren.

Die aus Sicht des Autors insbesondere von Prof. Dr. Franz Rößler und Dr. Wolfgang Hecker vorangetriebene Entwicklung machte es möglich, die Intel- und Zilog-Prozessorserien in Erfurt in kürzester Zeit effizient und fehlerfrei nachzubauen.

Ihren Höhepunkt erreichten die Arbeiten im Funkwerk Erfurt (MME) 1989 mit der Vorstellung der Kopie des 16-Bit Prozessors Intel 80286 als U80601 (IBM-PC-AT alias EC1835) [7] sowie mit der Nachentwicklung des ersten (leider einzigen) 32-Bit Prozessors der DDR U80701 (DEC MicroVAX KA78032 Prozessor-CPU als Kern der K1820-Rechner [8]). Beim Autor liegt ebenfalls die zugehörige FPU U80703 (alias DEC 78132) körperlich vor. Richard Kaussler war so freundlich, die Schaltkreise zu analysieren [16]. Es handelt sich auch hierbei um eine Nachentwicklung, bei der Details vom Original abweichen. Leider ist bislang unklar, wo die FPU nachentwickelt wurde. Für Hinweise wäre ich dankbar. Wir werden nicht jünger.

Der Autor wurde damals um Stellungnahme zu dieser herausragenden Leistung [4] gebeten. Ich wies auf ein Problem hin, daß noch Wochen zuvor unaussprechlich war. Die Einschätzung von Experten war plötzlich gefragt.

[1] Heinz, G.: nSGT - Entwurfsregeln Intel 8279. Vortragsfolien von 1979/80. (PDF)

[2] Heinz, G.: SIMPER-Katalog MOS-ED-Schaltungen (nSGT/NMOS) (PDF)

[3] Mead, C., Conway, L.: Introduction to VLSI-Systems. (download) (lokale Kopie)

[4] Berliner Meinungen zum 32-bit-Mikroprozessor. Berliner Zeitung vom 18.8.1989, S.2 (PDF)

[5] Rößler, F.; Fischer, P.; Möschwitzer, A.; Hecker, W.: LSISIMULATOR - ein leistungsfähiges Programm zu Funktionsverifikation hoch- und höchstintegrierter Schaltkreise. nte 34 (1984) H.6 213-214 sowie

Hecker, W.; Rößler, F.; Möschwitzer, A.: LSINET - ein neues Logik- und Timungsimulationsprogramm für LSI- und VLSI-Schaltkreise. Manuskript vom 6.5.1983, abgedruckt in nte 34 (1984) H.6 214-218.

(PDF)

[6] Heinz, G.: Grundzüge des höchstintegrierten Schaltkreisentwurfs (VLSI). INT Mitteilungen, Ausgabe A, 2-82, S. 13-27 (PDF). Die Auflage in 2000 Exemplaren wurde als NfD gestempelt und nur teilweise ausgeliefert. Eine Geschichte dazu siehe [12]

[7] DDR-Kopie des 16-Bit Prozessors Intel 80286 (als Kern des IBM-PC-AT alias EC1835). Wikipedia: MME U80601

[8] DDR-Kopie des 32-Bit Prozessors DEC MicroVAX II, KA78032 (als Kern der K1820-Rechner). Wikipedia: MME U80701; Bob Supnik (DEC): MicroVAX II (1985)

[9] Festschrift "100 Jahre Schwachstromtechnik" an der TU Dresden (Link)

[10] Layout des ersten, frei am Markt verfügbaren Mikrocontrollers Intel 4004 (Link)

[11] Jack Holloway, Guy Lewis Steele Jr., Gerald Jay Sussman, Alan Bell: The SCHEME-79 Chip. MIT, AI-Lab, AI-Memo No. 559, Jan. 1980. Ohne Copyright-Vermerk. Das Funktionsbild des SCHEME-79-Chips stellte das Titelbild der INT-Mitteilungen [6] des Autors dar.

[12] Heinz, G.: Zwischen den Fronten. Festrede zum Ausscheiden von Dr. Karl-Adolf Zech, genannt "Ali", aus dem Berufsleben. Abschiedsfeier am 14.12.2006 im Siemens-Werk für Signalbau, Elsenstraße, Berlin-Treptow (PDF)

[13] Hartenstein, R.W.: VLSI-Bausteine in geringen Stückzahlen für Spezial-Anwendungen. Elektronische Rechenanlagen, 22. Jahrg., 1980, H.4, S.159-173

[14] Hon, Robert W., Sequin Carlo H.: A Guide to LSI Implementation. Second Edition Jan. 1980, 158 p. XEROX PALO ALTO RESEARCH CENTER, 3333 Coyote Hill Road, Palo Alto, California, SSL-79-7. Dies war das Lehrbuch der 1978 beginnenden Mikroelektronik-Kurse zum MPC-Projekt, die das Ziel hatten, die Entwicklung von Mikrocontrollern zu vereinfachen und zu beschleunigen.

[15] The 1981 Achievement Award for "Introduction to VLSI-Systems" of Lynn Conway and Carver Mead. Mc Graw-Hill Journal "Electronics", Oct. 20, 1981, p.102-105

[16] Kaussler, Richard: Analyse der DEC MicroVAX II IC, die Nachbauten U80701 und U80702 im Vergleich zu den Originalen 78032 und 78132, siehe Link

[17] Wikipedia: Ersatzschaltungen des Bipolartransistors (Link)

Wer weiß mehr? Wer hat noch Materialien, Aufzeichnungen, Tagebücher?

Ergänzungen und Hinweise werden erbeten! Bitte an

info@gheinz.de senden!

Link auf diese Seite.

Visitors since Dez. 6, 2021: