Digitalisierung des Telefons:

Erste Schaltkreise aus Ost-Berlin

(Hauptstadt der DDR)

Fünf Jahre, bevor in Westberlin (BRD) der erste, integrierte Schaltkreis (IC) entworfen wurde, begann man im Institut für Nachrichtentechnik in Ostberlin (damals Hauptstadt der DDR) mit ersten Schaltkreisentwürfen. Das Zeitalter der Mikroelektronik hatte begonnen und veränderte die Fundamente der Welt. Industrieautomation einer neuen Qualität schuf enormen Wohlstand. Die US-amerikanische Weltspitze indes war längst enteilt.

Heute geht nichts mehr ohne Transistoren. Kaum ein Gerät kommt ohne Hunderte, Tausende oder Millionen und Milliarden von Transistoren aus. In jedem Haushalt werkeln unbemerkt hunderte Schaltkreise und Microcontroller mit hunderttausenden Transistoren für uns. In jedem USB-Stick, PC oder Smartphone stecken inzwischen Milliarden Transistoren. Allein eine Belichtungsmaschine für die Photolithographie kostet inzwischen eine halbe Milliarde Euro [173], [174].

Egal ob Netzteil, Fernbedienung, Uhr, Telefon, Schlagbohrmaschine, Radio, Fernseher oder Waschmaschine - nichts geht mehr ohne Mikroelektronik, ohne Transistoren, Mikrocontroller, Speicher oder kundenspezifische Schaltkreise. Für die Pioniere war es ein steiniger Weg voller Mühsal und Entbehrungen. Als Spinner belächelt, hatte man den eigenen Weg zu finden. Und man brauchte Mitstreiter.

Mit TTL-Schaltkreisen und ersten Ein-Chip

Operationsverstärkern begann Ende der 1960er Jahre die Mikroelektronik- Revolution. Spätestens mit dem erstem frei auf dem Markt verfügbaren Mikroprozessor, dem

Intel 4004, war ab 1971 die Tragweite dieser Entwicklung international nicht mehr zu übersehen.

_______

Die Vorgeschichte der Mikroelektronik ist lang. Der Däne Jakob Berzelius entdeckte 1824 den Halbleiter, der heute den Massenmarkt der Mikroelektronik dominiert, er nannte ihn Silizium.

Als Ferdinand Braun (bekannt geworden 1897 durch die Braunsche Oszillografen-Röhre) 1874 an der Uni Würzburg die Gleichrichtung (Diodeneffekt) entdeckte [131], war nicht abzusehen, welche Rolle Halbleiter in Zukunft spielen würden.

1885 entdeckte Clemens Alexander Winkler den Halbleiter, der die Massenproduktion erster, diskreter Transitoren und Dioden ermöglichte. Zu Ehren seines Heimatlandes nannte er ihn Germanium.

Julius Edgar Lilienfeld aus Lemberg (damals Österreich-Ungarn, heute Lwiw, Ukraine) ließ 1926 von Leipzig aus einen Feldeffekt-Transistor

(FET) patentieren "Methode und Apparat für die Steuerung elektrischer Ströme"

[126] mit Priorität in Canada Oct.22, 1925.

Siehe das Bild seines röhrenlosen Radioempfängers mit vier JFET-Transistoren, wie wir sie heute nennen würden. Er soll diesen Radioapparat über ein Jahr lang auf Ausstellungen vorgeführt haben. Sehr wahrscheinlich waren die Parameter der Transistoren noch nicht reproduzierbar, dh. Transistoren und Radio waren noch nicht serienreif.

Julius Edgar Lilienfeld aus Lemberg (damals Österreich-Ungarn, heute Lwiw, Ukraine) ließ 1926 von Leipzig aus einen Feldeffekt-Transistor

(FET) patentieren "Methode und Apparat für die Steuerung elektrischer Ströme"

[126] mit Priorität in Canada Oct.22, 1925.

Siehe das Bild seines röhrenlosen Radioempfängers mit vier JFET-Transistoren, wie wir sie heute nennen würden. Er soll diesen Radioapparat über ein Jahr lang auf Ausstellungen vorgeführt haben. Sehr wahrscheinlich waren die Parameter der Transistoren noch nicht reproduzierbar, dh. Transistoren und Radio waren noch nicht serienreif.

Er verglich die Eigenschaften seines Transistors mit denen von Röhren-Trioden. Wenn das Patent, wie in der anglo-amerikanischen Literatur behauptet, nur theoretischer Natur war, wie soll er dann die Kennlinien seiner Transistoren gekannt haben ("vergleichbar einer Röhren-Triode")? Und wie soll er seinen Radioempfänger zur Funktion gebracht haben? Undenkbar!

Ein Blick auf sein US-Patent 1745175 zeigt dem Elektroniker, daß diese Konstruktion durchdacht war und bis auf eine fehlende Diode, die aber auch über nichtlineare Kennlinien der Transistoren gebildet werden kann, funktioniert haben kann.

Es ist an der Zeit, einen fundamentalen, geschichtlichen Irrtum zu korrigieren. Lilienfeld war der Erfinder des Transistors. Und zwar bereits 1925, dreiundzwanzig Jahre vor den Nobelpreisträgern John Bardeen und Walter Brattain. Auch diese hatten 1948 noch lange keinen serienreifen Transistor anzubieten. Erste serienreife "Transistrons" kamen von Herbert Mataré. Bis 1954 waren seine Firmen die einzigen, die Transistoren produzieren konnten.

Zu Lilienfelds Zeiten waren noch keine Verfahren zur Einkristallzüchtung von Halbleitern verfügbar. Erst gegen 1960 wurde es möglich, Transistoren auf Einkristallen herzustellen. Das Problem sind vom Gitterwinkel abhängige, unterschiedliche Eindringgeschwindigkeiten und -tiefen von Dotierungssubstanzen, siehe Gitterführungseffekt, sowie Grenzflächenladungen zwischen Polykristallen. Deshalb experimentierte Lilienfeld mit dünnen Schichten amorpher Halbleiter, er nennt "copper sulfide" und "PbO" (Bleioxid). Heute werden Transistoren auf solchen Materialien realisiert, siehe z.B. organische Transistoren. In jedem Display eines Flachbildfernsehers oder eines Smartphons sind sie millionenfach verbaut.

An der Uni Leipzig verfügte Lilienfeld über ein eigenes Labor. Er hatte einen enormen praktischen Wissensschatz im Bereich von Physik und Chemie. Insbesondere kannte er sich mit Ladungsträgern und Feldeffekten aus. So erfand Lilienfeld den noch heute gebräuchlichen Elektrolyt-Kondensator, ein Bauteil, das 1998 einen weltweiten Umsatz von 6 Milliarden Dollar hatte.

Seine detaillierten Angaben zu Schaltungsdetails im Patent von 1926 sind zu präzise, um der Phantasie entstammen zu können. Die Quelle [137] zeigt, das es Messungen an funktionierenden Nachbauten gab, auch in den Bell-Labs.

Dennoch verschwanden die Lilienfeld-Patente aus dem kollektiven Gedächtnis. In der Wikipedia-Diskussionsseite zu Lilienfeld findet sich der Satz:

Der Halbleiterphysiker H. E. Stockman sagt "Lilienfeld hat seinen bemerkenswerten, röhrenlosen Radioempfänger bei vielen Gelegenheiten vorgeführt, aber Gott helfe einem Kerl, der damals die Herrschaft der Röhre bedrohte." Siehe dazu Bell Labs Memorial: "Wer hat den Transistor wirklich erfunden?", beginnend mit "Oscillating Crystals". (Quelle wurde offenbar gelöscht, 9/2023).

In der Biografie Lilienfelds heißt es:

"Als Brattain, Bardeen und ihr Chemikerkollege Robert Gibney versuchten, Patente auf ihre ersten Geräte zu erhalten, wurden die meisten ihrer Ansprüche aufgrund der Lilienfeld-Patente zurückgewiesen." [133]

Leider ist bislang wenig über Lilienfeld bekannt, die umfangreichste Recherche stammt von Prof. Dr. Christian Kleint von der Uni Leipzig [138].

Lilienfeld promovierte 1905 an der Friedrich-Wilhelm-Universität zu Berlin (heute Humboldt-Universität). Danach ging er an die Universität Leipzig zum Institut für Physik und habilitierte sich dort 1910. Bis 1925 arbeitete er dort auch an seinem Sperrschicht-Feldeffekt-Transistor (Junction-FET, JFET) (JFET), leider hatte er noch keinen Namen dafür, im Patent [126] spricht er von "relay or amplifier" und von "the invention". 1925 patentierte er diesen Transistor samt Radioempfänger (Priorität in Canada Oct.22, 1925). 1927 wanderte er in die USA aus.

Während sein erstes Patent [126] noch Schwachstellen zeigt und an Bastelei erinnert, gibt er im Patent [127] von 1928 dann eine praktikable Bauanleitung an, die für Mikroelektroniker nachvollziehbar ist. Aufgrund der Fülle beschriebener Details bestehen für den Autor nicht die geringsten Zweifel, daß Lilienfeld diese Transistoren prototypisch realisieren konnte, um eine so detaillierte Beschreibung liefern zu können.

Zu erwähnen sind zum Transistor weitere, deutsche Vorarbeiten und Patente von Oskar Heil 1934, [128], Walter Schottky 1938, [134], Rudolf Hilsch und Robert Wichard Pohl 1938, [129] und nicht zuletzt von Herbert Mataré und Heinrich Welker, die durch Kriegswirren behindert oder vernichtet wurden.

Oskar Heil entwickelte Lilienfelds Transistor weiter. Er stellt im Patent [128] das Prinzip heutiger, unipolarer MOSFET- Transistoren vor. Er führt den neuen Begriff "Semiconductor" (dt: Halbleiter) ein und definiert deren Eigenschaften. Heil studierte und promovierte 1933 an der Georg-August-Uni in Göttingen über Molekülspektroskopie. Nach Aufenthalten in England, in der Sowjetunion und wieder in England kam er am 2.9.1939 (einen Tag vor der britischen Kriegserklärung an Deutschland) nach Berlin zurück, um in der Lorenz-AG leistungsfähige Mikrowellen-Generatoren (Klystron) für Funkmess-Geräte (RADAR) zu entwickeln [136].

Kriegsbedingt wurden RADAR-Geräte zum Motor der Halbleiter-Entwicklungen - parallel in Deutschland, England und in den USA. Für den Wellenlängenbereich unter 10 cm waren Röhren für den Empfang ungeeignet, man begann, mit Halbleiterdioden zu experimentieren [136].

Herbert Mataré arbeitete schon 1942 mit sogenannten "Duo-Dioden" in Heterodyn- Empfängern (bipolare Spitzentransistoren), deren Verstärkereigenschaften umso besser wurden, je näher die Spitzen zusammen lagen, siehe die Mataré-Quellen von P. Salomon in [139], von Ch. Adam [140] "le transistron" und von Van Dormael "French Transistor" [136].

Die Ausrüstungen wurden aus Matarés Transistorlabor im März 1945 von der vorrückenden US-Armee aus der ehemaligen Thermometerfabrik "Goelitz" in Böhlen bei Großbreitenbach im Thüringer Wald abtransportiert. Wie wahrscheinlich ist es, daß sie in einem geeigneten US-Labor ankamen? Die Nachkriegswirren sorgten dafür, daß Mataré seine Arbeiten erst 1947 bei Westinghouse France in Paris fortsetzen konnte.

Mataré meldete zusammen mit Welker im August 1948 in Paris seinen Spitzentransistor an, den sie "transistron" nannten [132]. Am 21.4.1948 hatte Mataré bereits unter einem nichtssagenden Titel einen Legierungstransistor angemeldet [136], dessen Bauart später den Siegeszug der Massenproduktion von Transistoren einleitete.

Im Gegensatz zu den Bell-Labs konnte Matarè bereits 1949 Spitzentransistoren mit reproduzierbaren Eigenschaften liefern, die in Funkempfängern und als NF-Repeater in Telefonleitungen eingesetzt wurden [136], [140]. Auf der Düsseldorfer Funkausstellung im Augst 1953 wurde das welterste, batteriebetriebene Transistor-Radio mit Matarés Transistoren für den freien Markt vorgestellt [136]. Die US-Armee kaufte bis 1954 für Funkgeräte ausschließlich die Mataré Transistoren.

Bis 1953 waren Matarés Transistoren weltweit führend. Leider aber wechselten die Besitzer der Firma mehrmals und auch der Name der Bauteile. Damit geriet Matarés "transistron" ins Abseits und wurde für Jahrzehnte vergessen.

Vertraut man den Internet-Suchmaschinen und -Lexika, so entsteht das verzerrte Bild, als ob vor den späteren Nobelpreisträgern kein Transistor existierte [135]. John Bardeen und Walter Brattain konnten im Juni 1948 (US-Patent 2524035, [133]) einen Spitzentransistor anmelden. John Bardeen, Walter Brattain und William Shockley bekamen dafür 1956 den Nobelpreis für Physik und gelten bis heute (2023) als Erfinder des Transistors. Aber in Anbetracht der Vorarbeiten von Lilienfeld und Heil und der Einführung des Transistors von Mataré und Welker in die Serienproduktion erscheint diese Ehrung als vollkommen verfehlt.

Betrachten wir die wichtigsten Patente in ihrer Wirkung auf die weitere, technische Entwicklung der Mikroelektronik, so stechen einige Aspekte heraus:

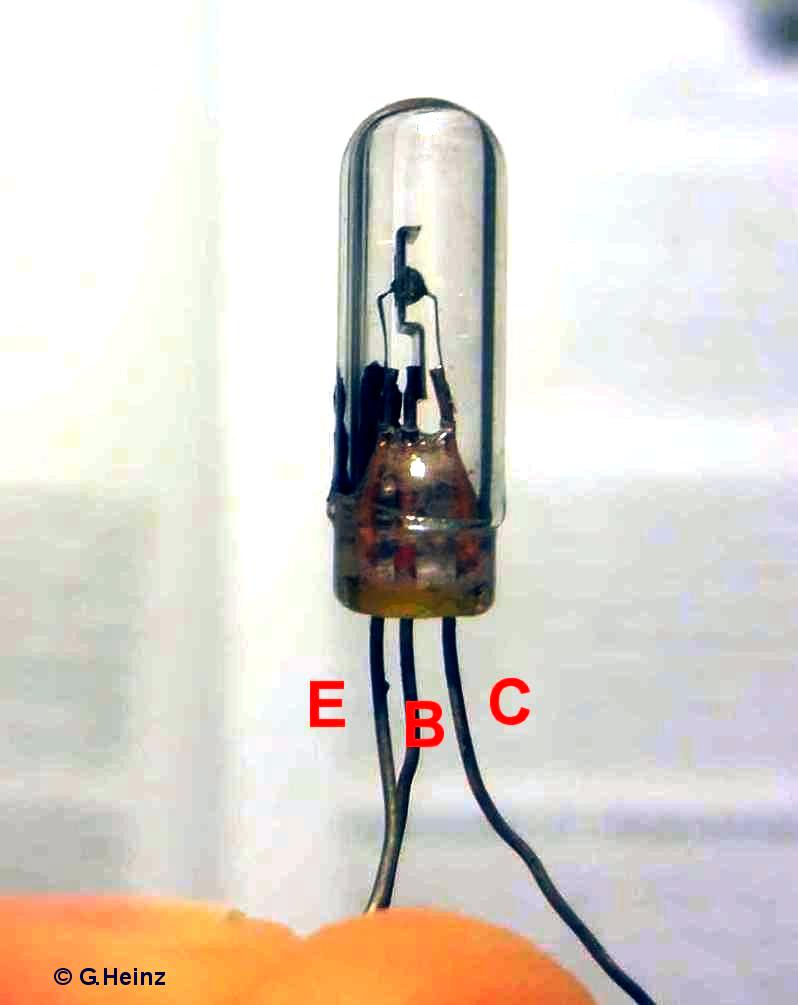

Bild 10: Einer der ersten (noch nach 65 Jahren funktionierenden) Germanium-Legierungstransistoren (vermutlich ein

OC601 von TFK, 1954). Das Gehäuse bestand aus einem schwarz lackierten Glaskolben, der Lack platzte ab. Elektroden v.l.n.r: Emitter, Basis, Kollektor.

Bild 10: Einer der ersten (noch nach 65 Jahren funktionierenden) Germanium-Legierungstransistoren (vermutlich ein

OC601 von TFK, 1954). Das Gehäuse bestand aus einem schwarz lackierten Glaskolben, der Lack platzte ab. Elektroden v.l.n.r: Emitter, Basis, Kollektor.

Spitzentransistoren spielten nur kurzzeitig eine Nebenrolle. Deren Parameter waren kaum reproduzierbar. Erst mit den in Serie einfacher beherrschbaren Legierungstransistoren (siehe Bild 10) begann die Mikroelektronik- Revolution. Sie eroberten in den fünfziger Jahren die Welt [62] und lösten innerhalb weniger Jahre auf vielen Gebieten die Elektronenröhre ab.

Zunächst waren die Transistoren für Funkempfänger und Verstärker interessant - mit im Vergleich zur Röhre winzigem Gewicht, Bauvolumen und Leistungsverbrauch. Auch arbeitete ein Transistor mit kleinen Spannungen (3 bis 9 Volt), die direkt einer kleinen Batterie entnommen werden konnten. Auch die Industrieautomation begann Fahrt aufzunehmen.

Erste Taschenradios arbeiteten als Audion mit einer selbsterregten Mischstufe. Man kam mit zwei Transistoren aus. Im Bild ist ein 2-Transistor-Audion (Life Tone, Boy's Radio Japan) vom Anfang der 1960er Jahre zu sehen. Heute undenkbar, erkennt man, daß zwei gewickelte Übertrager-Trafos offenbar billiger als zusätzliche Transistoren waren. Der Leser Heinz Gutbier schrieb dazu: "Mein erster Transistor war mit GTR gekennzeichnet, er entstammte der Reihe OC810 und kostete 13 Mark (der DDR)". Für diesen Preis konnte man damals vielleicht zehn Übertrager-Trafos erhalten.

Bild 11: Pendelaudion mit zwei Transistoren vom Anfang der 1960er Jahre. Die Originaltransistoren waren defekt und wurden ausgetauscht. Leider gab es schon 2014 keinen empfangbaren Sender auf Mittelwelle mehr (525 bis 1705 kHz, Amplitudenmodulation).

Plötzlich gab es tragbare Taschen- und Kofferradios. Die Jugend war fasziniert. Jeder schleppte seine "Kofferheule" mit sich herum. Aber Transistoren waren teuer. Mein erstes Taschenradio, einen russischer "Orbita" als Superhet mit 8 Transistoren, bekam ich 1968 zur Jugendweihe, der hatte 195 (DDR-) Mark gekostet. Viel Geld für damalige DDR-Einkommen!Zu dieser Zeit kostete ein OC821 im RFT-Bastlerladen in der Ostberliner Kastanienallee etwa 21 DDR-Mark. Bei 50 Pfennig Taschengeld war das unbezahlbar. Zum Glück aber hatten wir einen Mathe- und Physik- Lehrer, Eberhard Miegel, dessen Begeisterung für diese neuartigen "Transistoren" uns ansteckte. Er gründete 1967 an der 13. Oberschule Berlin-Heinersdorf eine Elektronik- Arbeitsgemeinschaft und besorgte nötige Bauelemente.

In der Arbeitsgemeinschaft berechneten wir als erstes die Widerstandswerte für einen astabilen Multivibrator (zu gebrauchen als Blinkgeber, Summer, Piepser etc.). In der Kastanienallee wollte ich die berechneten Widerstandswerte kaufen. Darunter zwei Widerstände mit 15625 Ohm. "Sowat ham wah nich!" antwortete die (Fach-) Verkäuferin. Ein älterer Herr hinter mir half: "Dann stückelste den Wert eben zusammen oder du nimmst den nächsten, runden Wert!". Der Multivibrator funktionierte schließlich auch mit gerundetem Wert ohne Probleme.

Bald gab es auch "Bastlertypen": Transistoren, deren Parameter leicht vom Datenblatt abwichen und die man ausmessen mußte. Die waren erschwinglich, man bekam sie für 50 Pfennige, später noch billiger. Meist hatten sie einen zu großen Reststrom, eine zu geringe Stromverstärkung oder andere Eigenheiten, man erinnere sich an den "SFT232".

Noch aber waren nicht mehrere Transistoren auf einem Substrat integrierbar. Dazu mußte erst die dielektrische Isolation in monolithischer Planartechnologie [72] erfunden werden. 1963 stellte Robert Noyce, einer der Gründerväter von Fairchild Semiconductor (1957) und Intel (1968), einen ersten monolithischen IC heutiger Bauart vor, auf dem 120 Transistoren galvanisch isoliert arbeiteten.

1963 stellte die Firma GTE-Sylvania unter der Bezeichnung SUHL (Sylvania Universal High Level Logic) das erste Sortiment von TTL-Schaltkreisen (Transistor-Transistor-Logic) vor. Recht schnell wurde das Sortiment von kapitalkräftigen Herstellern übernommen. 1964 ging der TTL-Schaltkreis SN5400 (4 NAND-gates a 2 inputs) von Texas Instruments in Produktion. TTL wurde ab 1966 durch die SN7400-Serie im DIP-Gehäuse (Dual Inline Package) populär.

Intel-Mitarbeiter Nr.12, Ted Hoff, begann 1968 am Befehlssatz des Intel 4004 zu arbeiten.

Das Jahr 1971 war ein besonderes Jahr für die Mikroelektronik. Bei Intel brachte man den ersten, auf dem freien Markt verfügbaren Mikroprozessor auf einem Chip heraus, den Intel 4004. Er hatte etwa 2300 Transistoren in p-channel Silicon Gate Technology pSGT (-15 Volt, 0.75 MHz, self aligned gates, negative logic). Niemand verstand, wie so ein Ding funktioniert und wozu man es brauchen kann. Es dauerte noch fünf Jahre, ehe es z.B. an der TU-Dresden die erste Vorlesung zu Mikrocontrollern gab.

Mit acht Jahren Verspätung wurde in der DDR 1971 die Geburt erster, digitaler Logikschaltkreise gefeiert: Im Halbleiterwerk Frankfurt/Oder (HFO) wurden erste bipolare TTL-Schaltkreise der Serie D100 (Nachbau des 7400) mit je 4 Transistoren und drei Dioden pro Gatter in SBC (siehe dazu auch [9] und [68]) produziert.

Im FWE gingen 1971 erste (wenig geliebte) unipolare Logik-Schaltkreise U101 bis U105, später bis U122 in Produktion (Vorbild-Serie MEM1000 von General Instrument, 1967). Diese hatten klassische PMOS Technologie (meist als EE Enhancement/Enhancement, als Lastwiderstand diente ebenfalls ein Enhancement-Transistor) mit zwei Betriebsspannungen -13 V und -27 V. Sie hatten negative Logik. Die Entwurfsregeln sind noch unter [79] zu finden. Der zeitliche Abstand der DDR zur Weltspitze (USA) betrug damals etwa 10 bis 14 Jahre.

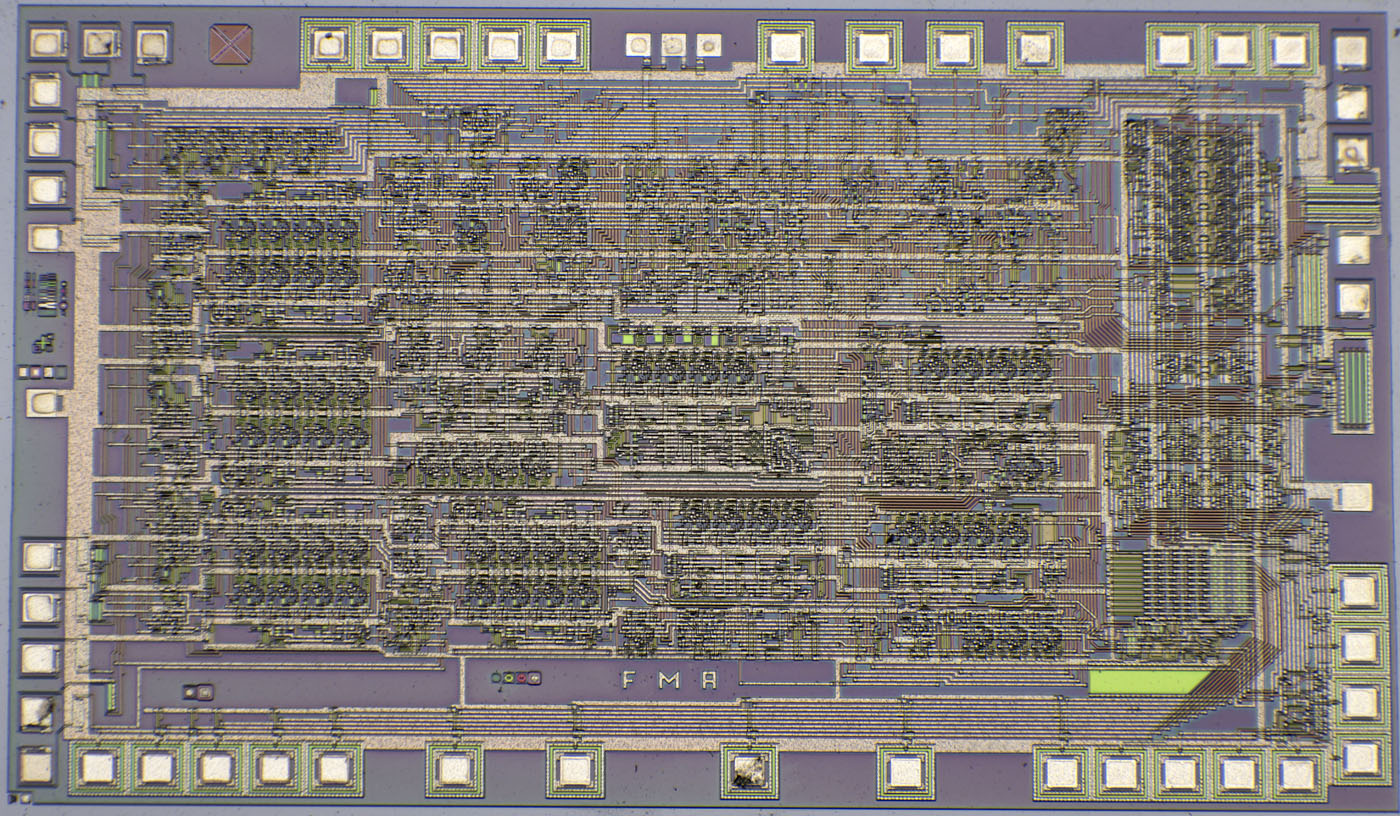

![]() Bild 12: Mit dem Erscheinen erster, digitaler ICs erschien auch der erste integrierte Analogschaltkreis der DDR, der Differenzverstärker IK72. Entwickelt wurde er für das Interkosmos-Programm des AdW Institut für Kosmosforschung (AdW-IKF) in Berlin-Adlershof (heute DLR). Er besaß drei Transistoren, eine Diode und einen Widerstand. Bilder mit freundlicher Genehmigung von Richard Kaussler, siehe auch die komplette Rückübersetzung auf seiner Seite [75].

Bild 12: Mit dem Erscheinen erster, digitaler ICs erschien auch der erste integrierte Analogschaltkreis der DDR, der Differenzverstärker IK72. Entwickelt wurde er für das Interkosmos-Programm des AdW Institut für Kosmosforschung (AdW-IKF) in Berlin-Adlershof (heute DLR). Er besaß drei Transistoren, eine Diode und einen Widerstand. Bilder mit freundlicher Genehmigung von Richard Kaussler, siehe auch die komplette Rückübersetzung auf seiner Seite [75].

Der IK72 bildete im Entwicklungszentrum des Halbleiterwerk Frankfurt/Oder (HFO) in Stahnsdorf den Ausgangspunkt für den ersten, kommerziellen Operationsverstärker A109 der DDR (Nachbau µA709), der ebenfalls 1972 auf der Leipziger Messe vorgestellt wurde (RFE 10/1972) und etwa ab 1974 marktverfügbar war.

Was damals noch niemand ahnte: die Mikroelektronik würde sich innerhalb weniger Jahrzehnte zur ersten, nur noch global funktionierenden Industrie dieser Erde entwickeln - mit Milliarden von Transistoren auf einem Chip. Heute (2018) enthält eine marktübliche 128 GigaByte (128 Milliarden Byte ~ 1000 Milliarden Bit) microSD-Speicherkarte (SLC) für rund 20 Euro einen Chip mit über 1 Billion (240 ~ 1012) Transistoren [73]. Kein Staat oder Unternehmen weltweit ist noch in der Lage, alle zur Produktion erforderlichen Spezialausrüstungen selbst zu entwickeln und zu produzieren. Allein die immer kürzer werdenden Wellenlängen in der Fotolithografie werden zum Albtraum, siehe [173] und [174].

Aber die RGW-Staaten hatten ein Problem: Das 1949 von den USA gegründete CoCom sollte den Technologieexport in kommunistische Staaten verhindern. Und CoCom funktionierte einschneidend. Der kalte Krieg hatte begonnen. Und alle Mikroelektronikprodukte fielen unter CoCom: Man konnte die meisten, neuen Schaltkreise nicht einfach importieren. Folglich hatte man sie nachzubauen - auch ohne Lizenz.

Letztlich aber hatte man in der DDR, wie auch in der Bundesrepublik oder in der UdSSR die aus den USA kommende Mikroelektronik zu wenig beachtet. Im Politbüro des ZK der SED erkannte man die technologische Revolution der Elektronik m.E. zu spät. Zitat Walter Ulbricht [1]:

"Nun Genossen, sagt mir doch mal, wieviel Tonnen Stahl

wir mit euern Transistoren mehr erzeugen können!"

Zentrale, planwirtschaftliche Leitung der Industrie hatte in der DDR dafür gesorgt, daß sich nur wenige Firmen mit Mikroelektronik beschäftigten. Dennoch gab es Pioniere, die unter schwierigsten Bedingungen damit anfingen [1], [76]. So wurde in der DDR mit einigen Jahren Verzögerung versucht, die Mikroelektronik-Revolution nachzuvollziehen. Von Anfang an war man in der Defensive, man entwickelte meist nach.

DDR, wie auch RGW waren technologisch im Hintertreffen. Eigene Entwürfe konnten noch so genial sein, sie scheiterten mit wenigen Ausnahmen an der Forderung der Industrie nach Kompatibilität mit im Westen bereits vorhandenen Bauelementen. Die Forderung war insofern berechtigt, als der pin- und schaltungskompatible Nachbau der ICs die Entwicklung von Software, von Leiterplatten und Mechanik parallel zur Schaltkreisentwicklung gestattete. Auch konnten erste Serienprodukte mit importierten IC bestückt werden, was eine schnellere Markverfügbarkeit bedeutete. Letztlich war man damit schneller, als mit einem Eigenentwurf.

Allerdings bedeutete die Kompatibilitätsforderung auch einen Generalverzicht auf innovative, neuartige Produkte, mit denen man viel mehr "Valuta" (Westmark oder Dollar) hätte erlösen können. Für Nachbauten, die noch dazu mit mehr als zwei Jahren Verspätung auf den Markt kamen, interessierte sich der Weltmarkt nur, wenn sie zu Dumping-Preisen angeboten wurden.

Beim Nachbau lief die DDR damit im internationalen Vergleich zu Höchstform auf. Im Halbleiterwerk Frankfurt/Oder [76] wurden sämtliche interessanten SBC-IC (bipolar) der Analogtechnik nachgebaut und produziert.

Eine noch größere Bedeutung aber kam wohl den im Funkwerk Erfurt (FWE), später Marx-Mikroelektronik Erfurt (MME) entwickelten Mikroprozessor- Systemen und deren Komponenten zu. Erfurt wurde zum wohl größten Erfahrungsträger außerhalb der USA auf diesem Gebiet. Neben dem Nachbau der Zilog Z80- Serie (CPU U880), der Zilog Z8-Serie (CPU U88xx) und der Zilog-Serie Z8000 (CPU U8001, U8002) gelang es, das Intel 80286 Prozessorsystem (IBM-PC XT; CPU U80601) sowie die microVAX II von DEC (CPU U80701) nachzubauen. Insbesondere diese CPU stellte allerhöchste Anforderungen an die Ingenieure des MME rund um den Chefentwickler Prof. Dr. Franz Rößler, weil der Chipsatz nicht marktverfügbar war. Es waren keine Spezifikationen erhältlich. Ausgehend von Chipfotos und Daten, die man einer (originalen) microVAX ablauschte, baute man eine "black box" nach.

Erste Berliner Schaltkreise wurden ab 1979 im Institut für Nachrichtentechnik (INT, [7]) in Berlin-Schöneweide, Hauptstadt der DDR (Ostberlin) entwickelt. Gefertigt wurden sie im Halbleiterwerk Frankfurt/Oder (HFO), im Zentrum für Mikroelektronik Dresden (ZMD) und im Funkwerk Erfurt (FWE -> MME). Bei ersten Schritten halfen DDR-Halbleiterhersteller mit. Zum Ende der DDR (1989) hatte das Entwurfszentrum Schaltkreisentwurf des INT unter Dr. Volker Tüngler etwa 65 Mitarbeiter (Hauptabteilung ECE [31]), weitere vier Entwurfszentren waren in Ost-Berlin im Entstehen, [32].

Das INT war das Forschungszentrum des VEB Kombinat Nachrichtenelektronik (KNE) mit 36.000 Beschäftigten in 19 Betrieben, siehe [63] Blatt 6 bis 9 und Profil in [46]. Mit 1640 Mitarbeitern (incl. Außenstellen 1987) war das INT das größte Institut der DDR.

Zur Geschichte des INT findet man unter [7] einen Abriß mit einigen, interessanten Bildern, insbes. zur OZ100. Wesentlichste Entwicklungsbereiche waren die Vermittlungstechnik (Vermittlungszentralen) und die Übertragungstechnik (Trägerfrequenz und PCM30/120/480/1920).

Das Telefonbuch des INT [33] gibt heute noch Aufschluß über die strukturelle Gliederung: Im INT waren alle Arbeitsgebiete vertreten, die mit Telefon, Funk und Nachrichten zu tun hatten. Gleich welches Wissen man brauchte: in irgendeinem Labor des Hauses war es verfügbar. Dieses deutschlandweit unvergleichliche Potential wurde dem Autor erst nach der Wiedervereinigung schmerzhaft bewußt. Aber es war das Wissen von einer Nachrichtentechnik, die vom Internet schnell überholt wurde.

![]() Institut für Nachrichtentechnik (INT, 1961-87),

Zentrum für Forschung und Technologie der Nachrichtentechnik (ZFTN, 1987-90), Direktoren:

Prof. Peter Fey 1961-1967, Dr. Peter Tietze 1967 bis 1969, Prof. Dr. Dietmar Lochmann 1969 bis 1986, Dr. Dietmar Bogk 1986 bis 1990. Umbenennung 1987 in ZFTN, 1640 Mitarbeiter (1987)

Institut für Nachrichtentechnik (INT, 1961-87),

Zentrum für Forschung und Technologie der Nachrichtentechnik (ZFTN, 1987-90), Direktoren:

Prof. Peter Fey 1961-1967, Dr. Peter Tietze 1967 bis 1969, Prof. Dr. Dietmar Lochmann 1969 bis 1986, Dr. Dietmar Bogk 1986 bis 1990. Umbenennung 1987 in ZFTN, 1640 Mitarbeiter (1987)

1160 Berlin (Oberschöneweide)

Edisonstr. 63

DDR

Fernsprecher 638-0

Fernschreiber INATE Berlin 112637

Drahtwort INATE Berlin

INT-Außenstellen (siehe [33] INT-Bereiche, S.7):

Allee der Kosmonauten 23A, Berlin 1136

Elsenstr. 106-107, Berlin 1193

Ewaldstr. 68-82, Berlin 1185

Nalepastr. 172, Berlin 1160

Singerstr. 109, Berlin 1020

Paul-Gruner-Str. 25, Dresden 8010

Schönbachstr. 90, Leipzig 7027

Sicherlich in Gedenken an die ungezählten Genies des INT ist heute, 2019, am Turm des Hauptgebäudes (Edisonstr. 63) eine Leuchtreklame "Leuchtenfabrik" angebracht. Erbaut wurde das Gebäude als "Lampenfabrik Frister" in Etappen von 1897 bis 1916; siehe [85]. Nach dem Konkurs von Frister 1933 ging das Gebäude an die Wärmegeräte GmbH, ab 1952 produzierte hier das VEB Funkwerk Köpenick. 1963 zog das INT ein.

Das Entwurfszentrum Mikroelektronik (EZµE) des INT wurde mit einem feierlichen Akt am 19.12.1979 unter Hauptabteilungsleiter Dr. Dietmar Bogk gegründet. Als Ziel wurde die Entwicklung kundenspezifischer Schaltkreise für die Nachrichtentechnik fixiert. Erste Bestellungen waren ein automatischer Vielfach-Sondentaster AVT 100 von Elektromat Dresden, ein Metallmikroskop Neophot 2 von Carl-Zeiss Jena und verzerrungsfreie Hostaphan-Folie (Mylar) für den Layoutentwurf als West-Import. Die Folien sollten aber erst vier Jahre später geliefert werden, als wir schon mit Graphikbildschirmen am KULON (PDP11-Nachbau) arbeiteten.

Erst zu diesem Zeitpunkt waren sie Bestandteil des Volkswirtschaftsplanes geworden. Bestellt waren ursprünglich 100 Blatt, vier Jahre später kam eine ganze Palette voll (etwa 3000 Blatt), Kostenpunkt der Folien 53.000 DM (Westmark) das waren rund 212.000 DDR-Mark. Zu diesem Zeitpunkt brauchte keiner mehr die Folien, sie wurden entsorgt. Die Einkäuferin erklärte mir Jahr für Jahr wieder, sie bekäme keine Mindermengen, jedesmal wurde dann die Bestellmenge erhöht. Meine Erkenntnis: So funktioniert staatlich organisierte Planwirtschaft.

Die ersten, kundenspezifischen Schaltkreise (ASIC) waren für die Digitalisierung des Teilnehmeranschlusses, die Übertragung vieler Telefongespräche auf einem Leitungspaar im zeitlichen Multiplex (PCM) [53], [54], [55], sowie für erste, digitale Vermittlungszentralen [48], [49], [50], [51], [52] bestimmt.

Bei folgenden Schaltkreis-Fotos gibt der Schaltkreis-Aufdruck Auskunft über Hersteller und Produktionsdatum.

Vorbei war das Zeitalter der analogen Telefontechnik. Das digitale Zeitalter sollte beginnen. Erst damit wurden Internet, Email oder SMS möglich.

Leider kam das Ende des INT mit der Wende unerwartet plötzlich. Den Mitarbeitern wurde gekündigt, im Tresor liegende Unterlagen flogen als NfD, VD, VS oder GVS aus dem Fenster direkt in riesige Müllcontainer auf dem Hof. Wenige Mitarbeiter wurden von SEL/ALCATEL übernommen. Zehntausende Datenblätter und Datenbücher folgten. Der Immobilienwert hatte über den Menschenverstand gesiegt. Über Nacht verschwand Menschenwissen und Menschheitsgeschichte in unvorstellbarer Dimension.

Zu diesen schreibt der letzte Direktor des ZFTN (INT), Dr. Dietmar Bogk:

"Die DDR hatte, wie auch die Bundesrepublik oder die UdSSR die aus den USA kommende Mikroelektronik verschlafen. Gewaltige erforderliche Investitionen sowie der fehlende Zugang zu den westlichen Technologiemärkten machten es für den sozialistischen Wirtschaftsblock extrem schwierig, diesen Rückstand aufzuholen. Die DDR versuchte diesen Nachteil bei der Bereitstellung weltmarktfähiger Produkte u.a. dadurch zu verringern, dass unter Umgehung der Embargomaßnahmen der USA technologische Ausrüstungen und Rechentechnik importiert wurden. Zusätzlich wurden ausgewählte Elektronische Bauelemente bis hin zu Speicherschaltkreisen und Mikroprozessoren importiert, zur Geräteentwicklung eingesetzt und gleichzeitig für eine Eigenproduktion vorbereitet. Damit ließ sich die Lücke zum westlichen Technologiefortschritt schneller schließen, da die Geräteentwicklung abgeschlossen war, bevor die Bauelemente aus eigener Produktion zur Verfügung standen. Die begrenzten Ressourcen sowie die erforderliche Geheimhaltung bei der Nutzung von Embargo- Technologien hatte in der DDR dafür gesorgt, dass sich nur wenige Firmen mit Mikroelektronik beschäftigten. Mit dem Fortschreiten der Integrationsgrade von Mikrochips kam diese Strategie aber an ihre Grenzen. Da zunehmend ganze Anwendungssysteme in die Chips wanderten, sah man sich in wachsendem Maße mit der Notwendigkeit konfrontiert, das Wissen um die Funktionen von Anwendungssystemen mit denen der Chipentwicklung zu verknüpfen. Im Institut für Nachrichtentechnik in Berlin hatte man diesen Trend frühzeitig erkannt und startete zeitweise gegen erheblichen Widerstand des zuständigen Ministeriums mit dem Aufbau eines Design- Zentrums für nachrichtenspezifische Schaltkreise. Dazu war es notwendig, engagierte Leute mit Weitblick und Engagement zu finden, die sowohl das Design von Schaltkreisen beherrschten, zusammenbringen konnten mit dem Entwickeln von Schaltungslösungen für integrationsfähige Systemkonzepte (z.B. eine Spule kann man nun mal nicht integrieren), als auch die erforderliche Rechentechnik und Softwarelösungen zum Design unter Embargobedingungen beschaffen, installieren und betreiben konnten. Und es fanden sich Pioniere, die unter schwierigen Bedingungen damit anfingen."

Das INT war Forschungszentrum des Kombinats für Nachrichtenelektronik (KNE), siehe ein Profil des KNE unter [180]. Die Kombinatsleitung saß bis 1987 im Fernmeldewerk Leipzig (FML). Siehe auch eine Übersicht zum FML in [114]. 1987 wurde das Funkwerk Köpenick (FWK) [178] zum Stammbetrieb. Zum 1.1.1988 wurde das INT zu einem Betriebsteil des Stammbetriebes FWK [179].

Aufsätze von Dr. Bogk in der Zeitschrift "Nachrichtentechnik, Elektronik" (nte) haben die damalige Situation konserviert. Im Aufsatz [3] sind Trends und Stand der Bauelementeentwicklung der DDR-Nachrichtentechnik beschrieben.

Die Aufsätze [5] und [6] repräsentieren den Stand der damaligen Produktentwicklungen der DDR-Nachrichtentechnik auf der Telecom87 in Genf und auf der Leipziger Frühjahrsmesse 1988. Insbesondere diese Quellen belegen, daß ein beachtlicher Entwicklungsstand erreicht wurde. Aber im internationalen Vergleich war die Entwicklung dennoch eher bescheiden zu nennen, siehe [96]. Reste der Entwicklungen sind noch zu besichtigen z.B. im Computermuseum Halle [2] oder im Fernmeldemuseum Dresden [48]. Eine letzte Umstrukturierung des VEB Kombinat Nachrichtenelektronik (KNE) vor der "Wende" mit dem Ziel der Effizienzsteigerung wird in [4] beleuchtet. Nicht zuletzt geben die Aufsätze [22] und [23] einen Überblick über damalige Arbeiten im INT.

Einen tieferen Einblick in den aus der historischen Perspektive eher hilflos wirkenden Versuch, die extrem dynamische und komplexe Entwicklung der Nachrichtentechnik planwirtschaftlich zu steuern, geben die Planungsvorlagen für den Ministerrat der DDR [46], [180...187]. Danach hätte die Produktion von digitaler Nachrichtentechnik auf Basis ISDN zu dem Zeitpunkt den Markt decken sollen (1997), als längst Netscape und Internet gefragt waren. Mit anderen Worten: Wenn die Leute nach dem Internet gerufen hätten, hätten sie endlich einen ISDN-Telefonanschluß (ohne Internet) erhalten können.

Wie unübersichtlich die Entwicklung der Mikroelektronik geworden war, zeigt ein Reisebericht des Chefkonstrukteurs des FWE, Franz Rößler, aus dem Jahre 1988 [84]. Zentrale Steuerung der Mikroelektronikentwicklungen wurde zunehmend unmöglich, weil niemand mehr die Komplexität der zu treffenden Entscheidungen überblickte. Bei der Lektüre des Berichts aus heutiger Sicht fällt auf, daß etablierte Hard- und Software kaum vorkommen, so taucht der Name "Cadence" nicht auf. Diese Firma mauserte sich in dieser Zeit zum weltweit führenden Anbieter von CAD-Software für den Schaltkreisentwurf. Auch wird dem IBM-PC kaum Beachtung geschenkt, der spätestens mit dem ersten PC-Internet-Browser "Netscape" im Jahr 1994 zur Nummer Eins des PC-Marktes wurde. Auch die damals weit vor "VHDL" stehende Hardware-Beschreibungssprache "Verilog" wird nicht benannt.

Das Grundproblem der planwirtschaftlichen Steuerung eines Wirtschaftssystems ist, daß man nicht vorhersagen kann, welche neuen Technologien in kurzer Zeit zur nächsten, technischen Revolution führen werden. So wurde immer wieder auf "Halde" produziert. Ressourcen wurden verschwendet.

Damals existierte noch keine Datenübertragung per Funk. Selbst bei utopischen Schriftstellern existierte noch nicht einmal die Vision eines mobilen Telefons heutiger Bauart (Touch-Display, Kameras, Telefon, Email, Internet-Browser, USB, LTE, GPS, WLAN, Bluetooth, NFC etc.). Ein Telefongespräch wurde analog übertragen. Jedes Gespräch benötigte dafür ein Adernpaar. Hin- und Rückkanal liefen auf diesem Paar, man trennte sie mit einer sog. Gabelschaltung auf beiden Seiten auf (Teilnehmer und Amt). Die Vermittlung erfolgte mittels mechanischer Relais-Schalter (Hebdrehwähler, Koordinatenschalter, zum Schluß Reed-Kontakte). Das Kapital der Telefongesellschaften waren 1980 die verlegten Kabel. Man rechnete, daß drei Viertel ihres Kapitals unter der Erde vergraben war. Mit dem Transistor entstand die Möglichkeit, mehrere Gespräche auf einem Adernpaar gleichzeitig zu übertragen: Im Frequenz- oder hier im Zeitmultiplex. Und man konnte damit stromfressende, große, schwere, teure und störanfällige Relais ersetzen.

Beim PCM30/32 System werden auf einem Adernpaar 32 digitalisierte Kanäle im zeitlichen Multiplex übertragen, zwei davon sind Dienstkanäle, deshalb die offizielle Bezeichnung PCM30/32.

Allerdings geht das nicht bidirektional, sondern nur unidirektional, pro verlegtem Adernpaar kann man nur je eine Richtung versorgen, über dieselbe Anzahl von Adernpaaren kann mit PCM30 folglich die 15-fache Zahl von Gesprächen geführt werden.

Jeder Abtastwert des Telefon-Analogsignals wird dabei in einem 8-Bit Wert gespeichert. Die analog-digital-Wandlung erfolgt nichtlinear nach µ-Law (Nordamerika, Japan) oder A-Law (Europa).

Zur Ablösung der analogen Telefonleitungen durch PCM wurden die etwa alle zwei Kilometer vergrabenen Pupin-Spulen durch PCM-Regeneratoren ausgetauscht. Pupin-Spulen dienten vorher der Entzerrung des Frequenzganges bei analoger Übertragung, nun dienten deren Behälter der Aufnahme der PCM-Regeneratoren.

Die Regeneratoren waren dabei gleichstrommäßig in Reihe geschaltet, der Spannungsabfall betrug 6,8 Volt pro Regenerator, der Speisestrom der Linie war mit 20 mA vorgegeben, [10], S.21. Eine Zenerdiode (6,8 Volt) sorgte für die Stabilisierung der Betriebsspannung jedes Regenerators. Leider existiert kein Schaltplan der ersten Version des Regenerators mehr.

Mit dem ersten Berliner Schaltkreis (IC), dem KA601, sollte ein großer, etwa 25.000 Mark teurer, mit diskreten Transistoren und Übertragern aufgebauter PCM30/32-Regenerator-Modul des VEB Nachrichtenelektronik Greifswald (NEG, Abteilung von Herrn Janke, Tel. 664556, letzte Beratung vor Überleitung ins HFO am 23.9.1980) durch zwei Schaltkreise (KA601 [60], [8], [9], [10] und KA602 [11]) abgelöst werden.

Vom Leistungsumfang entsprachen die ICs etwa dem, was 25 Jahre später unter dem Begriff "DSL-Modem" das Internet zu uns nach Hause brachte. Siehe auch eine detailierte Analyse des Chips von Richard Kaussler [110].

Mentor der Schaltkreisentwicklung war Dr. Ingomar Krahl. Er hatte an der TU Dresden auf dem Gebiet der bipolaren Transistormodellierung (Ebers-Moll und Gummel-Poon) sowie auf Integrierter Injektionslogik (I²L) bei Prof. Wolfgang Albrecht promoviert und brachte dieses Wissen zusammen mit Engagement, profunden Programmierkenntnissen und großer Offenheit und Herzlichkeit mit ins INT. Insbesondere brachte er das noch fehlende Wissen zu bipolarer Transistormodellierung (insbes. Gummel-Poon) mit, sodaß es mir möglich wurde, Baugruppen nicht nur als Kleinsignalmodelle mit Bleistift und Rechenschieber zu berechnen, sondern auch als Großsignalmodelle numerisch zu simulieren.

Die Berechnung der Leerlaufverstärkung des ersten Vorverstärkers VV1 lag z.B. nach der Erinnerung des Autors im Vergleich zwischen 68 und 71 dB (Handrechnung, numerische Kleinsignal-Simulation und Chipmessung). Der Autor setzte deshalb die Initialen "IK" vor die eigenen auf den Chip, Ingomar hatte maßgeblich dazu beigetragen, daß bereits von der ersten Version des KA601 (bis auf den falschen Kontakt siehe unten) nahezu alle Kennwerte perfekt erbracht werden konnten (Bildquelle [110]).

Die Berechnung der Leerlaufverstärkung des ersten Vorverstärkers VV1 lag z.B. nach der Erinnerung des Autors im Vergleich zwischen 68 und 71 dB (Handrechnung, numerische Kleinsignal-Simulation und Chipmessung). Der Autor setzte deshalb die Initialen "IK" vor die eigenen auf den Chip, Ingomar hatte maßgeblich dazu beigetragen, daß bereits von der ersten Version des KA601 (bis auf den falschen Kontakt siehe unten) nahezu alle Kennwerte perfekt erbracht werden konnten (Bildquelle [110]).

Unter Leitung von Dr. Dietmar Bogk organisierte Ingomar Krahl den fachlichen Aufbau des Entwurfszentrums: Nicht nur fähige und engagierte Mitarbeiter waren zu finden, auch Räume, Ausrüstungen, Gelder und Rechentechnik waren zu beschaffen. Das war nahezu unmöglich, da sämtliche Mittel nicht im Fünfjahrplan vorgesehen waren. Insbesondere erhielt das INT keine zusätzlichen Mittel für Gehälter der neu einzustellenden Mitarbeiter. So suchte man zunächst im eigenen Haus nach neuen Mitarbeitern. Auch waren Beschaffungen in Dollar oder D-Mark (DDR-Ausdruck "Devisen") zu machen, die im Plan nicht vorgesehen waren.

Unter Leitung von Dr. Dietmar Bogk organisierte Ingomar Krahl den fachlichen Aufbau des Entwurfszentrums: Nicht nur fähige und engagierte Mitarbeiter waren zu finden, auch Räume, Ausrüstungen, Gelder und Rechentechnik waren zu beschaffen. Das war nahezu unmöglich, da sämtliche Mittel nicht im Fünfjahrplan vorgesehen waren. Insbesondere erhielt das INT keine zusätzlichen Mittel für Gehälter der neu einzustellenden Mitarbeiter. So suchte man zunächst im eigenen Haus nach neuen Mitarbeitern. Auch waren Beschaffungen in Dollar oder D-Mark (DDR-Ausdruck "Devisen") zu machen, die im Plan nicht vorgesehen waren.

Im Rahmen einer Studie (Abschluß als Neuerervereinbarung NV7490 vom 29.8.1980) wurde im Januar 1980 im Bereich Ü (Übertragungstechnik) mit dem Systemkonzept des Gerätes PCM-Regenerator auf Basis KA601 [60] begonnen: Eilert: Systemeigenschaften, Behnke/Lohberger: Entzerrerverstärker; Höppner: Taktrückgewinnung, Neumann: Sendestufe. Die erste Beratung fand am 29.2.1980 statt (Kalendereintrag GH). Das Takt-Jitter der gesamten Regeneratorkette (maximal waren 18 in Reihe schaltbar) war zu minimieren, dazu wurde eine LC-Taktrückgewinnung favorisiert. Verstärkungen und Phasenspielräume der internen OPV wurden fixiert [10].

Ziel war, den PCM-Regenerator auf einem Master-Slice-IC (ISA) des Halbleiterwerks Frankfurt/Oder (HFO) zu entwerfen. Dies schien die preiswerteste, für kleine Stückzahlen taugliche Variante einer Realisierung als IC zu sein.

Der erste ISA-Master des HFO hieß IA60, er war in "Standard Buried Collector" Technologie (SBC) realisiert [9], [57], [68], [70], [71]. Bauelementeparameter des IA60-Masters und deren Simulationsmodelle sind unter [106] zu finden.

Bis zur Verfügbarkeit der unipolaren Technologien (PMOS, NMOS alias nSGT, CMOS alias CSGT) war die SBC-Technologie weltweit die grundlegende, (bipolare) Basistechnologie der Mikroelektronik, mit der sowohl erste digitale, als auch erste analoge Schaltkreise (man denke an SUHL/TTL siehe oben, OPV, Spannungsregler, Kleinleistungs-IC, IC für Kommunikation und Industrieautomation, I²L) produziert wurden. Der Umfang des Wikipedia-Eintrags 2021 zur SBC wird der Bedeutung für die weltweite Entwicklung der Mikroelektronik als Voraussetzung für den in den letzten 50 Jahren erreichten Wohlstand durch Industrieautomation und Informatik nicht gerecht: Jeder unbekannte Künstler oder Politiker oder Dauer-Subventionsempfänger ist dort hundertmal wichtiger als dieses Basiswissen der Mikroelektronik als Quelle unseres Wohlstands.

Die Schaltungsentwicklung begann neben Restarbeiten zum Übungsprojekt Intel 8279 (siehe Aufsatz "Wie alles begann") im Februar 1980. Schaltungsentwurf, Berechnung, Simulation und Layout lagen beim Autor [68], Systemkonzept und externe Beschaltung unterstützten insbesondere Manfred Höppner (ÜL2), Hans-Uwe Behnke (ÜL3) und Dr. Manfred Brandes (ÜL1).

Idelles Vorbild waren die hervorragenden Applikationsschriften und Datenblätter [95] der Schaltkreise EXAR XRC262 und XRC277. Beide Schaltkreise, das legten Richard Kausslers Recherchen [110] erst 2024 nahe, waren von EXAR offenbar ebenfalls auf einem Vorbild des IA60-Masters realisiert worden.

Die Schaltungen des KA601 [10] und KA602 [11] waren letztlich den EXAR-Schaltungen des XRC262 recht ähnlich. Leider blieben die Originalschaltungen (und Berichte) des KA601 (Versionen 1 und 2) und des KA602 nicht erhalten. In den Bericht [10] von 1981 wurden nachträglich unleserliche Korrekturen von 1984 eingeklebt. Im Bericht [11] sind die originalen Schaltungen durch Korrekturen von 1983 ersetzt.

Um die Spreu vom Weizen trennen zu können, sind im ersten Test auf der Siliziumscheibe Messungen mit Sondentaster erforderlich. Dazu müssen Tester programmiert werden. Es wurde ein kleines Team (ECE3) aufgebaut zur Entwicklung der Prüftechnik und der Simulationsprogramme unter Günther Warme und Volker Otto, siehe [31].

Anläßlich des Besuchs einer Tesla-Delegation hielt der Autor am 23.4.1980 einen ersten Vortrag zum Konzept und zu den Vorbildern des geplanten PCM-Regenerators, den IC XRC262 und XRC277 von EXAR [95]. Da im Tausch gegen Erdöl und Erdgas 70% der Nachrichtentechnik der DDR nach der Sowjetunion ging, wurden extreme Temperaturanforderungen gestellt (+80...-40°C).

Erste Rechnungen zeigten, daß gegenüber den XRC-Lösungen zusätzliche Stabilisierungsmaßnahmen von Strömen und Spannungen erforderlich waren (Kalendereintrag vom 11.7.80). Daraus entstand das Patent "Schaltungsanordnung fuer kombinierte, temperaturstabile Referenzspannungs- und Referenzstromquellen" (als Bestandteil des KA601) [44].

Der erhöhte Schaltungsaufwand brachte ein Problem mit sich: Während Exar die Schaltungen des XRC266 und des XRC277 auf die Größe des Masters abstimmen konnte [110], mußte der Schaltkreis auf zwei IA60-Master (KA601 und KA602) aufgeteilt werden. Der Analogteil KA601 enthielt Operationsverstärker und Analogelektronik, der Digitalteil KA602 die digitalen Latches und Endstufen, siehe Bild 22.

Am 11.6.1980 war der Abschlußbericht der Neuerervereinbarung NV7490 fällig, am 12.6.1980 wurde das Konzept im HFO der Entwicklungs-Leiterin Erika Godau im "Roten Salon" im Halbleiterwerk Frankurt/Oder vorgestellt (Kalendereintrag GH).

Im Entwicklungsbereich war unter Leitung von Erika Godau (EE) und Fritz Schackow (EEC) durch Gerhard Neugebauer und Hanno Fulde (EECA) ein Master-Slice-System IA60 ("Meisterscheibe") nach dem "Monochip"-Vorbild von Ferranti [64] entstanden, siehe Details dazu bei Richard Kaussler unter [110].

Mit Transistoren und Widerständen belegte Chips werden dabei auf einem Silizium-Wafer vorproduziert, der Kunde kann in der obersten Ebene eine einlagige Verdrahtung (in Aluminium) gestalten. Mit diesem System ließen sich kleine Stückzahlen kundenspezifischer Schaltkreise schnell und kostengünstig produzieren. HFO hatte keinerlei freie Entwurfskapazitäten, man konnte nur ein VT100-Terminal zur Verfügung stellen, der Kunde hatte Layoutprüfungen mit der HFO-Software selbst zu machen.

Von Hanno Fulde und Gerhard Neugebauer (HFO) erhielt ich den auf Millimeterpapier geplotteteten ISA-Master IA60, siehe [9], [57], [68]. Er war auf viertel Millimeter als Ganzes geplottet. Mit Bleistift wurde der Alu-Layer des Kunden (INT) darauf konstruiert. Der Entwurf wurde dann an einem Robotron-Zeichenbrett mit Lupe auf 1/4 mm digitalisiert. Dabei entstanden etwa 2000 Abstandsfehler.

Die Überleitungsberatung zum PCM-Regenerator fand am 10. Oktober 1980 im Halbleiterwerk Frankfurt/Oder (HFO) statt. (Neben dem Entwurfszentrum des HFO wurde auch ein nagelneuer "Tester 2000" besichtigt, eine Eigenentwicklung aus dem HFO; Kalendereintrag GH).

Bild 20: Der Autor bei der Arbeit an einem Testfeld am Digitalisier-Zeichenbrett "Robotron REISS DIGITRON" (um 1980). Daneben stand ein Orgautomat Daro-Optima 528 mit zwei Displays NC410 sowie einem Lochbandstanzer. Rechts: Bild eines Daro-Optima 528 mit Lochbandleser und Bedienkonsole aus dem Computermuseum Halle.

Die Daten liefen über zwei Display-Einheiten

NC410

mit Nixie-Röhren (sie zeigten die aktuelle x- und y-Koordinate an) parallel zu einem Orgautomaten

(Daro Optima 528) mit einem Lochbandstanzer. Mit dem Druck auf den zentralen Drehknopf des Zeichenbretts wurden x- und y-Koordinate gestanzt, der Stanzer machte dann ein Geräusch der Art "Ratteldibum", da mehrere Byte (x-Koordinate und y-Koordinate) hintereinandergestanzt wurden.

Die Daten liefen über zwei Display-Einheiten

NC410

mit Nixie-Röhren (sie zeigten die aktuelle x- und y-Koordinate an) parallel zu einem Orgautomaten

(Daro Optima 528) mit einem Lochbandstanzer. Mit dem Druck auf den zentralen Drehknopf des Zeichenbretts wurden x- und y-Koordinate gestanzt, der Stanzer machte dann ein Geräusch der Art "Ratteldibum", da mehrere Byte (x-Koordinate und y-Koordinate) hintereinandergestanzt wurden.

Manchmal waren die Arbeitsbedingungen hart. In einem Kalendereintrag notierte der Autor: "Da im Institut keine Räume frei waren, wurde ein fensterloser, ehemaliger Kohlenkeller umgerüstet. Im Winter 1979/80 gab es Probleme mit der Heizung, es war jämmerlich kalt (14°C)." Die Fernwärme aus dem nebenan liegenden Heizwerk des BMHW (Berliner Metallhüttenwerke) fiel aus. Dem BMHW waren die Kohlen ausgegangen.

Nebenbei bemerkt, standen damals kaum Möglichkeiten zur Verfügung, Kopien von Berichten oder Aufsätzen herzustellen. Schrieb man selbst einen Bericht, so wurde dieser von der Abteilungs-Sekretärin i.a. auf Pergamentpapier abgetippt. Fehler wurden mit einem Glashaarpinsel herausradiert und mit der Schreibmaschine korrigiert. Formeln, Bilder und Zeichnungen wurden mit einem Scribent mit schwarzer Ausziehtusche nachgetragen. Sonderzeichen in Formeln

(z.B. Ω, ω, ∑, ∫ ) waren auch mit Scribent nachzutragen. War der Bericht fertig, lief man damit in die Ormig-Abteilung des INT. Dort stank es gewaltig nach Ammoniak. Man erhielt dann violette, wenig kontrastreiche Kopien, die sich kaum noch kopieren ließen. Bekam man ein Original in die Hände, so bettelte man bei der Sekretärin des Hauptabteilungsleiters (Dr. Richter, folgend Dr. Bogk und zuletzt Dr. Tüngler), das Thermokopiergerät (Bild rechts) benutzen zu dürfen. Amerikanische Laser-Kopierer waren erst gegen Ende der DDR vorhanden.

Nebenbei bemerkt, standen damals kaum Möglichkeiten zur Verfügung, Kopien von Berichten oder Aufsätzen herzustellen. Schrieb man selbst einen Bericht, so wurde dieser von der Abteilungs-Sekretärin i.a. auf Pergamentpapier abgetippt. Fehler wurden mit einem Glashaarpinsel herausradiert und mit der Schreibmaschine korrigiert. Formeln, Bilder und Zeichnungen wurden mit einem Scribent mit schwarzer Ausziehtusche nachgetragen. Sonderzeichen in Formeln

(z.B. Ω, ω, ∑, ∫ ) waren auch mit Scribent nachzutragen. War der Bericht fertig, lief man damit in die Ormig-Abteilung des INT. Dort stank es gewaltig nach Ammoniak. Man erhielt dann violette, wenig kontrastreiche Kopien, die sich kaum noch kopieren ließen. Bekam man ein Original in die Hände, so bettelte man bei der Sekretärin des Hauptabteilungsleiters (Dr. Richter, folgend Dr. Bogk und zuletzt Dr. Tüngler), das Thermokopiergerät (Bild rechts) benutzen zu dürfen. Amerikanische Laser-Kopierer waren erst gegen Ende der DDR vorhanden.

Auf das Plotbild des Masters aus dem HFO wurde mit Bleistift das Layout gezeichnet. Weil der Master auf viertel Millimeter genau geplottet war und der Entwurf nun auch auf viertel Millimeter digitalisiert werden mußte, entstanden Unmengen an Eingabefehlern. Eine Vierteilung des Entwurfs war noch nicht möglich, HFO hatte noch kein Programm zur Verfügung, um die Stücke wieder zusammensetzen zu können.

Zur Abhilfe entwickelte unsere erste Software-Entwicklerin Christiane Krahl für die Version 2 des KA601 ein 4x4-Punkt Papier-Entzerrungsprogramm für die Koordinaten, um den Papierverzug vor der Digitalisierung zu reduzieren. Vor Arbeitsbeginn waren nun stets 16 Referenzpunkte für die spätere Entzerrung einzugeben. Da eine Layoutfigur nicht doppelt digitalisiert werden sollte, wurde jede erfaßte Leitbahn-Figur im Master-Plot mit Buntstift markiert.

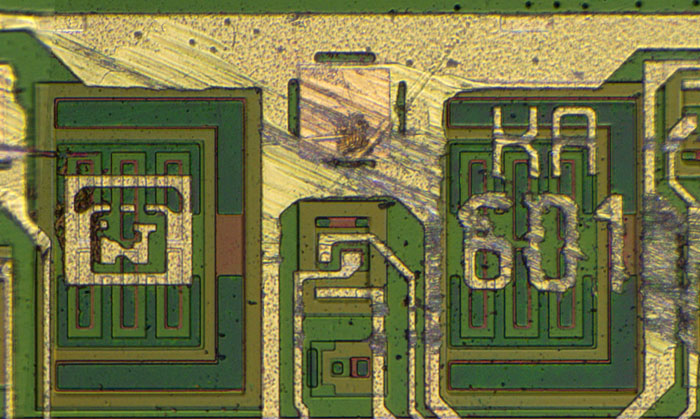

Bild 21: Ausschnitt aus dem Plotbild des Masters IA60 (magenta) mit der Alu-Kundenmaske eines KA601 (schwarz). Die Chipgröße betrug 2,6x3,0 mm. Alle Transistoren maßen 110x140µm. Siehe auch die Analyse von Richard Kaussler [110]. Rechts: Lochband-Reparaturgerät NISA.

Je nachdem, wie weit man kam, entstanden an jedem Arbeitstag einige Lochstreifen-Stückchen, diese wurden mittels Lochband-Reparaturgerät (Bild rechts) aneinander geklebt. Nach dem Verkleben stanzte man die Löcher (Bits) an der Klebestelle u.U. manuell nach. So entstand allmählich eine Lochbandrolle mit dem kompletten Layout.

Im Oktober 1980 brachte der Autor das fertige Lochband ins Halbleiterwerk Frankfurt/Oder (HFO), um die Einhaltung der Entwurfsregeln zu prüfen. Ein Layoutprüfprogramm gab es im HFO bei Hanno Fulde und Co. auf einer DEC-PDP11 bereits, aber weder Grafikbildschirm noch Grafikeditor. Alles passierte mit einem Texteditor (TECO oder EMACS?) und ASCII.

Um sich vorstellen zu können, wie dies ging, hier eine kurze Schilderung.

Auf dem Lochband waren die Absolutkoordinaten jedes Punktes in der Form (x,y) gespeichert. Zunächst wurde ein Lochband-Leseprogramm gebraucht, um den Datensatz vom Lochband auf die Festplatte zu kopieren. Im zweiten Schritt wurde bereits ein intelligentes Programm gebraucht, um daraus eine kompakte Orthogonaldarstellung der Differenzen in der Form (x0 y0; dx1 dy1; dx2 dy2;... ; dxn dyn \r\n) zu machen. Damit begann jede neue Figur auf einer neuen Zeile. Im dritten Schritt konnte bereits die erste Entwurfsregelprüfung erfolgen: Zu kleine dx oder dy wurden sogleich als Entwurfsfehler gelogt, weil sie auf windschiefe Geraden hindeuteten. Da nur orthogonale Geraden und 45-Grad Diagonalen erlaubt sind, war sogleich eine Summenprüfung möglich: Die Summe aller x- und aller y-Koordinaten einer Figur mußte Null ergeben. Nun, das erste Logfile enthielt - wen wundert es - gleich einmal zweitausend Fehler, die nun in dem mehrseitigen ASCII-Listing zu suchen waren. Allein die GND-Figur war eine Seite lang. Um ehrlich zu sein: Nur mit einem Texteditor bewaffnet, war es sehr harte Arbeit.

Um sich vorstellen zu können, wie dies ging, hier eine kurze Schilderung.

Auf dem Lochband waren die Absolutkoordinaten jedes Punktes in der Form (x,y) gespeichert. Zunächst wurde ein Lochband-Leseprogramm gebraucht, um den Datensatz vom Lochband auf die Festplatte zu kopieren. Im zweiten Schritt wurde bereits ein intelligentes Programm gebraucht, um daraus eine kompakte Orthogonaldarstellung der Differenzen in der Form (x0 y0; dx1 dy1; dx2 dy2;... ; dxn dyn \r\n) zu machen. Damit begann jede neue Figur auf einer neuen Zeile. Im dritten Schritt konnte bereits die erste Entwurfsregelprüfung erfolgen: Zu kleine dx oder dy wurden sogleich als Entwurfsfehler gelogt, weil sie auf windschiefe Geraden hindeuteten. Da nur orthogonale Geraden und 45-Grad Diagonalen erlaubt sind, war sogleich eine Summenprüfung möglich: Die Summe aller x- und aller y-Koordinaten einer Figur mußte Null ergeben. Nun, das erste Logfile enthielt - wen wundert es - gleich einmal zweitausend Fehler, die nun in dem mehrseitigen ASCII-Listing zu suchen waren. Allein die GND-Figur war eine Seite lang. Um ehrlich zu sein: Nur mit einem Texteditor bewaffnet, war es sehr harte Arbeit.

Von Ende Oktober bis Weihnachten 1980 arbeitete ich dann im HFO, um die Fehler (meist die digitalisierten Viertelmillimeter) mittels Texteditor auf einem VT100-Terminal an der PDP11 zu beseitigen. Man fuhr täglich im ungeheizten Zug von Berlin nach Frankfurt/Oder hin und zurück. "Für die paar Pendler lohnt es sich nicht, den Zug zu heizen" verkündete der Schaffner. Verfroren, manchmal hustend oder schnupfend zurück zu Hause in Berlin-Pankow hatte man Kohlen aus dem Keller zu holen und den Ofen zu heizen. Erst eine Stunde später wurde es warm im Zimmer. Heute, im Zeitalter der Zentralheizungen unvorstellbar: Man fror im Winter oft erbärmlich - ein Zustand, den die heutige fridays4future - Jugend vielleicht noch kennenlernen will.

Bild 22: Blockschaltung von KA601 (li.) [10] und KA602 [11] (re.). Man erkennt beim KA601 fünf Operationsverstärker, sowie zwei Blöcke zur Erzeugung stabilisierter Referenzspannungen. Der KA602 enthält zwei D-Latches, Strobe-Erzeugung und Gegentakt-Endstufen. Siehe auch den HFO-Werkstandard der IC KA601 und KA602 [60] und die Vorbilder von EXAR [95].

Dieser erste IC des INT (KA601) war nicht nur der erste Berliner IC, sondern auch der erste Kundenschaltkreis der DDR und das erste DDR-Gate-Array in klassischer Bipolar-Technologie (SBC). Damals war der Begriff Gatearray noch nicht üblich, man sprach von Master-Slice.

Layoutabschluß war unmittelbar vor Weihnachten 1980 im HFO. Im Frühjahr 1981 erhielten wir erste Muster. Leider wurden zunächst alle Chips beim Scheibentest als Ausschuß mit rotem Farbklecks markiert, Reste davon sind noch auf dem Chipfoto zu erkennen. Nun war guter Rat teuer. Wie finden wir den Fehler? Letztlich hatten die Chips [8] [10] einen Kontakt zuviel, der im HFO unter dem Mikroskop mit einem Spezial-Laser ausgebrannt werden konnte, siehe Bild 23. In Version 1 entstanden damit 5 funktionierende Chips. Um mehr über Transistoren und Technologie zu erfahren, lohnt sich auch ein Blick in Richard Kausslers Analyse des KA601 unter [110].

Bild 23: Ein fehlerhafter Kontakt in Version 1 konnte mit einem Laser ausgebrannt werden (Bildmitte). Bild von Richard Kaussler [110]. Rechts: Auszug Plotbild der ersten Version vom 6.3.1981.

Die Chips wurden in der hauseigenen Hybridtechnik (Horst Schulenburg) auf ein Glassubstrat (Bild 23) gebondet. Wie zu erwarten, gab es Probleme mit einfallendem Licht. Version 2 wurde in ein DIL24-Gehäuse gebondet. Erst später folgte ein DIL18-Gehäuse.

Siehe dazu ein Layout und Plotbild des KA601 [8] sowie Blockschaltung, Bondschema, Innenschaltung, Plotbild und Layoutfoto [10].

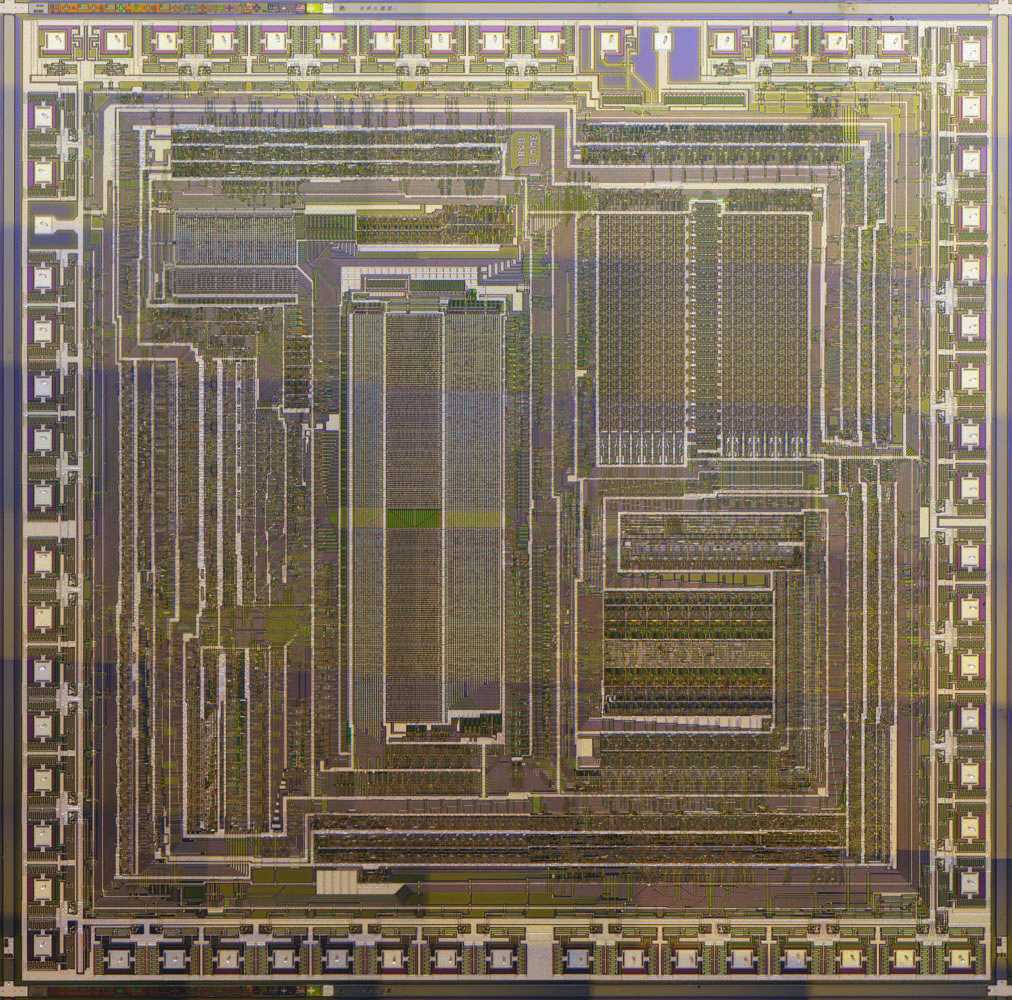

Bild 24: Chipfoto vom KA601 Version 1 vom März 1981. Neben der Typbezeichnung ist die Layer-Nummer "1", ein INT-Telefon und die Kürzel "IK" und "GH" im Alu-Layer zu erkennen. Klick auf das Bild: Fotografie eines reparierten Chips von Richard Kaussler. Siehe auch hochauflösende Detailaufnahmen des KA601 auf seiner Seite [110].

Mitarbeiter und Berater: Systementwurf, Regelungstechnik und Filtertheorie: Manfred Höppner u.a.; OPV-Simulationen mit Stadynet (PL/1): Gerd Heinz, Helfried Geupel, Beate Fiedler; Transistor-Modelle: Ingomar Krahl; Schaltungstechnik und Layout (V1 und V2: Gerd Heinz, folgende Versionen: Dr. Volker Tüngler; Zyklus II: Volker Tüngler, Horst Schulenburg (Glasträger); Testprogramme und Pincards: Volker Tüngler, Volker Otto, Technologie Master-Slice: Gerhard Neugebauer (HFO), Hanno Fulde (HFO); Berechnungen, Schaltungstechnik, Simulation und Layout: Gerd Heinz; Ideelle Basis bildeten die ICs EXAR262 und EXAR277 [95], siehe auch [8], [9], [10], [11], [68].

Bild 25: KA601 V2. V1 und V2: Gerd Heinz; V3 bis V5 Dr. Volker Tüngler

Bild 26: links: Plot KA601 V4: Dr. Volker Tüngler; rechts im 18-poligen DIL-Gehäuse 01/1985

Bild 27: KA602 V2, Digitalteil PCM-Regenerator. Schaltungsentwurf: Gerd Heinz, Systemeinbindung Manfred Höppner; Layout V1 und V2: Dr. Volker Tüngler [11]. Kein Layoutfoto vorhanden. Gehäuse von 04/1983.

In Auswertung der Testprobleme wurde u.a. ein Schaltkreistester von Schlumberger aus Frankreich beschafft, mit dem die Funktion von Schaltkreisen einfacher getestet werden konnte einschließlich der Möglichkeit zur Testung direkt auf dem Chip. Dazu wurde im INT eine kleine Arbeitsgruppe für Prüffolgenentwicklung und Schaltkreistest unter Volker Otto aufgebaut.

Mit diesen ersten zwei IC war im Institut für Nachrichtentechnik erstes Wissen zur Entwicklung eigener Schaltkreise entstanden. Erste Schaltkreise der Version 2 wurden durch NEG (Nachrichtenelektronik Greifswald) in eine PCM-Versuchsstrecke eingebaut (wo?). Diese lief viele Jahre und wurde erst gegen Ende der neunziger Jahre abgebaut (Quelle verschollen - bitte hilf mit!). Wahrscheinlich sind keine Exemplare des PCM-Regenerators als Baugruppe erhalten - oder?

Erfahrungen mit dem Entwurf des KA601 flossen später in den Entwurf eines universellen ZF-Verstärkers und Demodulators KA630 für Polizeifunk durch Thomas Birke vom Funkwerk Köpenick ein [109].

Erstmals in meiner kurzen Berufslaufbahn fühlte ich mich richtig wohl. Version 2 des KA601 und Version 1 des KA602 funktionierten. Ich konnte mich mit Simulation und Parameteroptimierung der Stromquellen (Ebers-Moll-Typ), der spannungsabhängigen Kapazitäten und manueller Nachrechnung der OPV, der Temperaturgänge und dem Jitter der LC-Schwingkreise austoben. Das Thema lag mir, als uns 1981 über Ali Zech das Buch von Mead/Conway [26] erreichte.

Verbunden mit einer Gehaltserhöhung erhielt ich vom damaligen Hauptabteilungsleiter Dr. Bogk 1981 den Auftrag, ein VLSI-Team für den Entwurf der im Bereich Vermittlungstechnik entstandenen Pflichtenhefte für Schaltkreise einer großen IDN-Zentrale zu bilden. Die kurze Phase größter Arbeitsfreude war vorbei. Dr. Tüngler hatte die ICs KA601 und KA602 zu übernehmen, um Anpassungen an erweiterte Kundenvorgaben zu machen. Für den VLSI-Schaltkreisentwurf waren Mitarbeiter zu gewinnen und zu qualifizieren, [34].

Wie in allen Bereichen der Technik geht es international darum, schneller und besser als die Konkurrenz zu sein. Worin bestand dieses "schneller und besser" in der Nachrichtentechnik?

Außer Braunkohle, Salz und Uran besaß die DDR kaum Rohstoffe. Die Wirtschaft war in hohem Maße importabhängig. Im Verhältnis zu einer elektronischen Zentrale wog eine mit Relais arbeitende etwa zehn bis zwanzig mal soviel pro Teilnehmer. Ein Großteil des Gewichts der Relaisspulen steckt im Kupfer der Spule und im Eisenkern. Aber besonders der Preis für Edelmetalle für die Relaiskontakte bereitete in der DDR große Probleme. Auch ist die Verlustleistung von Relais um ein vielfaches höher, als die von Transistoren. Volumen und Gewicht elektromechanischer Zentralen lagen um ein vielfaches höher, als bei späteren, elektronische Zentralen. Somit war der Übergang zur elektronischen Vermittlungstechnik für die DDR überlebenswichtig.

Der Einstieg dazu kam über die PCM30/32 Übertragungstechnik. 1972 stellte das Fernmeldewerk Leipzig (FML) auf der Leipziger Frühjahrsmesse ein erstes PCM30/32 Übertragungssystem aus. Auf derselben Messe hatte CIT-Alcatel die PCM-Technik bereits mit elektronischer Vermittlungstechnik gekoppelt und stellte die erste elektronische Zentrale aus. In Lannion (Frankreich) hatte man die erste sogenannte ISDN-Insel aufgebaut siehe [160], S.43, Abb.45.

Relais brauchen Kontakte, die nicht oxidieren. Dafür werden große Mengen an Edelmetallen gebraucht. Auch brauchen Relais Unmengen an Kupfer für die Relaisspulen. Edelmetalle wie auch Kupfer sind teuer. Sie waren oft nur gegen Devisen zu haben. Folglich ging die technische Entwicklung in Richtung der Verkleinerung und Gewichtsreduktion der Relaiskontakte, nicht nur in der DDR.

Während im Jahre 1891 Almon Strowger's Erfindung des Hebdrehwählers mit dem zwanzig Jahre später erfundenen Nummernschalter im Telefonapparat eine geniale Einheit bildete [175] (als Impulswahlverfahren IWV), ist beim Koordinatenschalter [176] (z.B. in der ATZ65, S65, MSN70) eine Umsetzung der IWV-Pulse [156] auf die anzusteuernden Zeilen- und Spaltenrelais erforderlich. Dazu nutzte man einen sogenannten Zählmagnet oder Relaisketten, die als Zähler geschaltet waren.

Der Einsatz von Reedrelais (nur ein Kontakt pro Relaisspule) erforderte dann eine komplett elektronische Steuerung. Bei ENSAD wurde aus dem Großrechner ESER R55 (IBM360 kompatibel) eine spezielle Lösung zur Steuerung der Reedrelais SK3410 abgeleitet [177]. Die Reedrelais dienten nur noch der Durchschaltung der analogen Telefongespräche, nicht aber der Steuerung der Anlage.

Gewichtseinsparungen wurden in der Nachrichtentechnik weltweit in Etappen realisiert. Von der Handvermittlung über ein Steckerfeld hin zum Drehwähler und Hebdrehwähler (Siemens System22), über Koordinatenschalter (ATZ65) auf Reedkontakte (ENSAD). Zum Schluß erst kam der Transistorschalter. Aufgrund der nichtlinearen U/I-Kennlinie aller Transistoren mußten alle Gespräche vorab digitalisiert werden. PCM30/32 war das geeignete Mittel der Wahl.

Mit den glasgekapselten Reed-Kontakten stieg die Zuverlässigkeit elektromechanischer Koppelfelder. Die Kontakte konnten nicht mehr korrodieren. So entstand in den 1970er Jahren das teilelektronische Vermittlungssystem ENSAD [56], [165], das bereits mit elektronischer Steuerung auf der Basis von RTL/TTL/CMOS-Schaltkreisen und Reed-Kontakten als Analogschalter softwaregesteuert arbeitete (vergleichbar mit dem System EWS-A von Siemens). ENSAD wurde nur für die UdSSR produziert und soll keine Postzulassung der DDR gehabt haben [160] S.121, [165].

Zentrales Problem war die Bauelementebeschaffung. ENSAD wurde beständig weiterentwickelt, ich erinnere mich an Kollegen Arnold Rost von der Abteilung VT, der eine ENSAD-Karte zum siebenten mal mit neuen Bauelementen zu realisieren hatte. Im Tausch gegen Erdöl wurde ENSAD zwar in großem Umfang, aber hauptsächlich für den Export in die Sowjetunion produziert. 139 ENSAD-Zentralen wurden von Robotron und Fernmeldewerk Arnstadt ausgeliefert.

Nun kann man Transistoren nicht als direkten Ersatz für Relais nutzen, sie haben nichtlineare, "krumme" Kennlinien und würden durchlaufende Gespräche viel zu stark stark verzerren.

Vorab hat man das Analogsignal mit Analog-Digitalwandlern (ADC) zu digitalisieren. Aus einem Abtastwert (der momentanen Höhe des Analogsignals) werden nun 8 Bit, die sehr viel schneller übertragen werden können. Abgetastet wird noch heute mit 8 kHz und 8 Bit. Pro Telefonkanal und pro Richtung sind damit 8x 8kHz = 64 kb/s (Kilobit pro Sekunde) zu übertragen.

Da auf einer Leitung sehr viel mehr als 64 kb/s übertragen werden können, schachtelt man viele Gespräche ineinander, die Pulscodemodulation (PCM) entstand zunächst als Übertragungstechnik insbesondere zwischen Vermittlungszentralen. Je nachdem, wieviele Kanäle pro Leitungspaar übertragen werden können, spricht man von PCM30, PCM120, PCM480, PCM1920 usw.

Damit spielte die PCM auch in der Vermittlungstechnik sofort eine entscheidende Rolle. Betrachten wir viele PCM-Leitungen, so ist ein Gespräch dort genau auf einer Leitung (Raumlage) und dort wieder genau in einem Zeitabschnitt (Zeitlage) zu finden.

Eine innovative, völlig neue Art von Vermittlungstechnik entstand. So braucht eine Fernzentrale mit 100 kommenden und 100 gehenden PCM30- Leitungen ~ 3000 laufende Gespräche für etwa 10.000 Anschlüsse (AE) plötzlich nur noch die Raum- und Zeitlagen der Kanäle zu vertauschen, um Gespräche zu vermitteln.

Um Kosten zu sparen, versuchte man (wie wir heute wissen) in der Vermittlungstechnik recht erfolglos, Entwicklungen im Rat für gegenseitige Wirtschaftshilfe (RGW) abzustimmen.

Im RGW favorisierte man zentral gesteuerte Anlagen mit PCM32-Multiplexer der Art Siemens EWSD [143]. Diese setzten sich letztlich auch durch.

In der DDR glaubte man an den Erfolg des dezentral organisierten System 12 von ITT/Alcatel mit digitalen ISDN-Telefonen [146].

Mit dem digitalen ISDN-Anschluß (Basic-Rate-Interface BRI) des Telefons [147] liebäugelten EWSD [143] und System 12 gleichermaßen. Allerdings erwies sich eine digital-Umstellung von 3,3 Millionen bislang analoger Teilnehmerapparate (DDR 1983) als volkswirtschaftlich undenkbar. Auch ist dem Autor bis heute kein DDR-Telefon bekannt, das einen digitalen ISDN-Anschluß (Zwei- oder Vierdraht, UK0 oder S0) geboten hätte [147].

Allerdings gab es noch vor dem Ende der DDR einen ersten ISDN-Call. Rolf Siemon verließ das INT 1988 und ging ins IIR (Institut für Informatik und Rechentechnik der AdW). Auf Basis seiner Dissertation hatte ein Kollege dort einen multifunktionalen ISDN-Schaltkreis entwickelt (persönliche Kommunikation).

Nach ENSAD [160] S.121, [165], [56] - einer halbelektronischen Großzentrale mit Reed-Relais - und parallel zu westlichen Entwicklungen wie Siemens EWSD [143] oder ITT/Alcatel System 12 entwickelte eine kleine Systemgruppe unter Rolf Siemon im größten Bereich des INT für Vermittlungstechnik (Dr. Peter Tietze) ab 1979 ein eigenes, vollelektronisches Vermittlungssystem für große Ortszentralen namens IDN (Integriertes, Digitales Netz), die zum Ausgangspunkt der DVS/DVZ- Zentralen (Kap.10.4) wurden. Anleihen davon waren beim ITT/Alcatel System 12 genommen worden.

Es entsprach in wesentlichen Leistungsmerkmalen dem ISDN. Absehbar in der DDR ungenutzt bleibende Dienstmerkmale, insbesondere die digitale Telefonschnittstelle, blieben ausgeklammert. Es wurde eine Art "ISDN-light". ISDN war im IDN auf für DDR-Verhältnisse realistische Funktionen, insbesondere für den analogen Telefonanschluß reduziert. Vorrangig sollten vorhandene, analoge Telefone unterstützt werden sowie die digitale (PCM-) Anbindung an kleine Zentralen und an digitale (PCM-) Fernzentralen.

Digitale (ISDN-) Telefone standen bis zum Ende der DDR nicht zur Verfügung. Bei diesen befindet sich der Codec/Filter-Komplex im Telefon. Weil das Kapital der Telefongesellschaften in der Erde lag, war man interessiert, vorhandene Zweidrahtleitungen zu nutzen. Eine bidirektionale, digitale ISDN-Zweidrahtleitung hätte nach einer zusätzlichen, speziellen Echokompensation verlangt. Dieses Problem wollte man sich noch ersparen.

Auch stand eine lange Tradition des deutschen Fernsprechwesens im Wege. Bis dahin wurden alle Telefone vom batteriegepufferten Amt gespeist, um auch bei Stromausfall telefonieren zu können. Das war als eine Art "Grundgesetz" unantastbar. Im Gegensatz dazu müssen ISDN-Telefone aus dem Netz gespeist werden. So kann man bei großflächigen Havarien nicht mehr kommunizieren.

Eine Eigenentwicklung war insofern möglich, als die Fachzeitschriften dieser Jahre voll von Artikeln über die Planungen und über die Entwicklung digitaler Netze war, auch die Entwicklungen zum ISDN (mit digitalen Telefonen) konnten von unseren Systementwicklern verfolgt werden, da die INT-Hausbibliothek auch wichtige Westzeitschriften und Bücher führte.

Im Mittelpunkt des Projekts standen aber die analogen Telefone. Millionen von ihnen sollten weiterhin nutzbar bleiben. ISDN-Dienstmerkmale waren für analoge Telefone kaum interessant. Die Integration von Telefon- und Datenverkehr hingegen schon.

Pflichtenhefte für eine IDN-Ortszentrale und drei PCM30-Kunden-Schaltkreise (IEMS, ESES, IKOS) sowie für deren Umfeld waren ab 1979 von Rolf Siemon und Kollegen (Bereich V - Vermittlungstechnik) und Mitarbeitern, wie Thomas Wehren geschrieben worden. Die Funktion der verschiedenen Einheiten, die Schnittstelllen ins Netz und zum Teilnehmer, sowie Aufgaben für die Softwareentwicklung waren definiert. Die Arbeiten begannen an den Schaltkreisen noch 1981. Geistiges Vorbild für die IC-Entwicklung wurden die revolutionären Datenpfad-Architekturen in [26], Kap.4 und 5.

Analog zum System 12 von ITT sollte das zu entwickelnde PCM30/32 Koppelfeld drei kundenspezifische IC besitzen:

Der ungekrönte "Chefentwickler" der drei ICs, Thomas Wehren, kam aus dem Bereich Vermittlungstechnik und hatte bereits an einer diskreten Realisierung eines PCM-Koppelfeldes mitgewirkt.

Das großartige Buch von Carver Mead (Caltech) und Lynn Conway (Xerox Corp.) "Introduction to VLSI-Systems" [26] kam 1981 genau richtig, um die Arbeiten am IDN enorm zu beschleunigen. Dieses Buch brachte eine Revolution in den Designprozess integrierter Schaltkreise. Man denke an das Multichip-Project (MCP, Kap.4), oder an Dave Johannsens OM2-Machine (Kap.5 in [26]). Sie zeigten, wie man Entwurfseffizienz durch Wiederholstrukturen um ein Vielfaches steigern kann. Dr. Karl-Adolf Zech gelang es, das Buch in der DDR zu popularisieren. Der Aufsatz [13] des Autors diente auch dem Anliegen, auf diese Entwicklung in den USA aufmerksam zu machen.

Anmerkungen:

Im Gegensatz zu einer Leiterplatte kann man in einem IC nur ganz wenige Signale beobachten, nämlich die, die auf Pins nach außen geführt sind. Wie aber kann ermittelt werden, welcher Schaltungsteil im Fehlerfall defekt ist? Hier gab ein Mitarbeiter wertvolle Hilfe, der sich Westkontakte nicht verbieten ließ. Dr. Karl-Adolf Zech schulte zum "Design for Testability" [34], [37]. Er kommunizierte privat mit westlichen Wissenschaftlern [38] und ließ sich deshalb auch zu keinerlei Geheimnisschutz verpflichten (jede Geheimnisschutzverpflichtung beinhaltete in der DDR i.a. den Verzicht auf Westkontakte). Er war es, der 1980 auf das alles verändernde Buch von Mead/Conway "Introduction to VLSI-Systems" [26] aufmerksam machte (VLSI: Very Large Scaled Integration).

Nach Mead/Conway sahen digitale, hochintegrierte Schaltkreise anders aus, man vergleiche dazu mit einem IC aus der Zeit vor M/C. Mead/Conway hatten Wiederholstrukturen zur Einsparung von Entwurfszeit popularisiert, vereinfachte Layout-Entwurfsregeln (lambda design tools) eingeführt und die Gatterdynamik strukturiert, siehe [13], [19], [26], [39], [74], [115].

Dr. Zech "Ali" erhielt u.a. auch vom MIT und vom Caltech enorm wertvolle Papers zu Designs für Mikrocontroller, PLA, RAM, ROM, AD-Wandler, Filtertheorie etc. Der von Dr. Zech verfolgte Plan, das Buch von Mead/Conway ins Deutsche zu übersetzen, gelang nicht. Wir hatten viele prominente Befürworter (u.a. auch Dr. Bogk) gefunden, die das Vorhaben aktiv unterstützten. Wir hatten die Kapitel aufgeteilt, meine Kapitel waren bereits übersetzt, da kam die Absage vom Verlag Technik.

Dr. Zech setzte 1981 eine Rezension in die Zeitschrift Messen-Steuern-Regeln "msr" und konnte damit sogar Kontakt zu Carver Mead aufnehmen [144], dem aufgrund des Buches damals wohl bekanntesten Mikroelektroniker der Erde [145]. Das ist etwa so, als würde man heute (2024) Kontakt zu Elon Musk aufnehmen wollen, um fachliche Details über seine E-Autos oder Reketenentwicklungen zu erhalten: Es dürfte kaum jemandem gelingen.

Leider verließ Ali 1983 das INT [43]. Er hatte immer wieder Ärger wegen seiner fachlichen Kontakte in die USA und nach Westdeutschland, zugleich auch wegen seines kirchlichen Engagements (z.B. für "Schwerter zu Pflugscharen"), er gab schließlich auf und ging zum Werk für Sicherungstechnik und Signalbau (WSSB) in der Elsenstraße, welches nach der Wende 1989 von Siemens übernommen wurde.

Mead/Conways Ansätze zur Gatterdynamik wurden weiterverfolgt [20], daraus entstand die Dissertation [45] des Autors.

Ali hatte sich in den Jahren bis 1983 unermüdlich Papers amerikanischer Elite-Universitäten zu neuesten, integrierten Schaltungstechniken, Modellen und Methoden (nSGT, CMOS) zusenden lassen, die für den Aufbau des Entwurfszentrums nützlich waren. Er geriet ins Visier der Staatssicherheit, als er 1980 mit dem Abzeichen "Schwerter zu Pflugscharen" am Arbeitsplatz erschien. Fast wäre der Autor über diese Freundschaft zu Ali gestolpert, auch ein U-Haft Einlieferungsantrag fand sich in meinen Stasi-Unterlagen, siehe dazu [43].

Nun lebte der Vater des Autors als Arzt in Westberlin. Parteisekretär, Personalstelle, MfS und Abteilung ST hegten permanentes Mißtrauen. So hatte der Autor alle halbe Jahre wieder einen "Kaderbogen" auszufüllen, in den alle Westverwandschaft einzutragen war. Immer wieder wurde er von der Kaderleiterin Frau Pieplow ermahnt, die Adresse des Vaters einzutragen. Meine Mutter hatte den Kontakt zum Vater nach dessen "Republikflucht" 1961 abgebrochen. So hatte auch ich bis zur Wende weder die Adresse, noch Kontakt zu ihm. Auch forderte der Abteilungsleiter ST (Tarnname im Telefonbuch: Bereich S Software, Abteilung T Technik) den Autor bei jedem fachlichen Kontakt freundlich, aber energisch auf, seine Kontakte zu Dr. Karl-Adolf Zech ("Ali") abzubrechen.

Da die Entwicklung kaum Vertraulichkeit besaß (NfD - Nur für Dienstgebrauch), konnte die Entwicklung zwischen beteiligten Entwicklern ungehindert kommuniziert werden. So war es mir dann 7 Jahre später auch möglich, Bilder dieser IC-Eigenentwicklung im Buch "MOS-VLSI-Technik" von Wolf-Dieter Fischer und René Schüffny 1987 zu publizieren, siehe Beitrag und Layouts in der Anlage von [19] sowie [74].

Aber wir hatten zunächst weder geeignete Computer, noch Terminals, noch Plotter (der PC war noch nicht interessant). Zunächst stand nur ein russisch/bulgarischer PDP11-Nachbau KULON mit zwei über eine serielle Schnittstelle angeschlossenen Terminal-Arbeitsplätzen mit grünen Speicherbildröhren zur Verfügung, der mehrschichtig genutzt wurde.

Die Arbeitsbelastung war riesig, Geld fehlte an allen Ecken und Enden. Wie kompliziert die Situation war, zeigt ein Stasi-Bericht [104] von 1982. Allerdings sollte dieser nicht überbewertet werden, denn nur wo gehobelt wird, fallen auch Späne. Oder wie Horst Bosetzky sagte: "Unter jedem Dach wohnt auch ein Ach."

Für die nSGT2-Entwürfe übernahmen wir die Idee der Lambda-Entwurfsregeln von Mead/Conway [26], die auf die nSGT2-Technologie [34] des potentiellen Herstellers der IC, ZFTM Dresden, angepaßt wurden [28], [58], [59], [74]. Mit diesen wurde es möglich, schneller und mit einem gröberen Raster zu arbeiten. Noch lieber hätten wir M/Cs Stick-Layouts genutzt, aber dazu fehlte der Vorlauf in der Software.

Durch die Lambda-Entwurfsregeln sank automatisch die Rate der Layoutfehler und der Entwurf jedes Layouts wurde beschleunigt. Auch wurde die rechentechnische Regelprüfung beschleunigt. Rechenzeit war damals sehr kostbar, die Rechner hatten winzige Hauptspeicher, Plattenspeicher und Rechenleistungen. Man vergleiche dazu die Plotbilder in [19] und [74] mit Vorbildern von M/C [26].

Federführend beim Eigenentwurf von 1981 bis 1984 waren Rolf Siemon (System) und Thomas Wehren (Datenweg-Planung und Layout). Mitarbeiter: Regina Rösener, Arnold Rost, Gerd Heinz u.a., siehe Reste in [19] und

[74].

Bild 31: IEMS-Ausschnitte vom Dezember 1983 aus [19]. Oben: Layoutnaher Logikplan, darunter das Layout. In einer Zusatzebene wurde das Logiksymbol der Datenpfadzelle gespeichert. Um zwischen Layout und Logik umzuschalten, wechselte man einfach die Ebenen. Entwurf: Thomas Wehren, Gerd Heinz, Regina Rösener, Arnold Rost(?), Gerhard Seeger(?).

Bild 32: Genormte Kompositzellen für die Datenpfadarchitektur von IEMS, ISES und IKOS (nSGT2, 1982) aus [74]. Plotts unseres russischen Folienschneiders, der zum Einfarb-Plotter umgerüstet wurde.

Zur statischen Dimensionierung der nSGT-Gatter wurde ein Arbeitsblatt entwickelt. Damit konnten die B/L-Verhältnisse der Enhancement- und Depletion-Transistoren der Gatter effizient bestimmt werden [58], S.12.

Meine Aufgabe bestand darin, die dynamischen Parameter der SRAM-, ROM- und PLA-artigen Datenpfad-Strukturen zu verifizieren. Es war sicherzustellen, daß die Baugruppen nicht zu groß und zu langsam wurden, entsprechende Bit-Verstärkerschaltungen waren zu entwickeln, die Datapath-Dynamik war zu verifizieren, die Schaltungen war dynamisch zu partitionieren.

Leider existiert nur vom IEMS ein Plotbild vom Dezember 1983, das mangels eines eigenen Plotters geplottet wurde im Werk für Fernsehelektronik (WF) nebenan: Download [159] (39 MB).

Die ersten zwei IC (PCM-Sende- und PCM-Empfangsschaltkreis) waren 1983 bereits mit spärlichsten Mitteln (KULON und ESER) bis auf einige Verifikationen fertig entwickelt, einzig der Koppelfeldschaltkreis war noch nicht fertig, als 1984 unerwartet eine von oben verordnete Wende kam.

Vorausgegangen war das Scheitern einer Bilanzierung der drei ICs im ZMD oder FWE auf dem kleinen Dienstweg "von unten". Man hatte keinerlei Kapazitäten im KME, die drei ICs (IDN-PCM Sender, Empfänger und Koppelfeld) in die Produktion überzuleiten.

Zum Verständnis: Ein Vermittlungsnetz, bei dem die Signalübertragung digital erfolgt, wurde auch international als integriertes Digitalnetz (IDN - Integrated Digital Network) bezeichnet. Ein Digitalnetz für verschiedene Typen von Kommunikationsschnittstellen wird als dienstintegrierendes Digitalnetz (ISDN - Integrated Services Digital Network) bezeichnet. Solche Schnittstellen konnten typisch sein:

Die drei Schaltkreise sollten nur die Datenfluß- Funktionen (dataflow) bedienen, die permanent abliefen, nicht aber die Funktionen, die man mit Mikroprozessoren eleganter lösen konnte. Im wesentlichen sollten analoge Teilnehmer und Verbindungen zu Nebenstellen sowie Orts-, wie Fernzentralen über PCM bedient werden.

Leider erfolgte 1984 eine Kehrtwende. Die Schaltkreisentwicklung wurde abgebrochen, mit dem fatalen Ergebnis, daß die Schaltkreise auch für die DVZ2000 nicht rechtzeitig zur Verfügung standen, vgl. Kap.7 und Kap.10.4. Den Verantwortlichen war nicht bewußt, welchen Arbeits- und Zeitaufwand eine IC-Entwicklung mit damaligen Mitteln kostete.

Der Begriff ISDN [147] stand in den 70er Jahren als Abkürzung für "Integriertes Sprach- und Datennetz". Mit internationaler Verbreitung wurde die Abkürzung umgedeutet in "Integrated Service Digital Network" (Dienstintegriertes, Digitales Netz). Kern der Bemühungen war ein einheitlicher Kommunikationsstandard für jegliche Sprach- und Datenkommunikation.

Mit ISDN sollten unabhängige Netze für Telex, Datex (nur BRD), Datenpakete und Telefonie vereinheitlicht werden. Standleitungen für Rechner-Datenaustausch waren extrem teuer und ineffizient. Sie sollten abgebaut werden.